MARCH 2018 REV. 1.0.2

#### GENERAL DESCRIPTION

The XR28V382 (V382) is a dual Universal Asynchronous Receiver and Transmitter (UART) for the Intel Low Pin Count (LPC) bus interface. This device can replace or supplement a Super I/O device to add additional serial ports to the system.

The V382 UARTs support any 16-bit I/O address supported by the system. The register set is based on the industry standard 16550 UART, so the V382 operates with standard serial port drivers without requiring a custom driver to be installed.

The 128 byte Transmit and Receive FIFOs reduce CPU overhead and minimize the chance of buffer overflow and data loss. In addition to the 16550 UART registers, there are also Configuration register set where enhanced features such as the 9-bit (multidrop) mode, IrDA mode and the Watchdog Timer can be

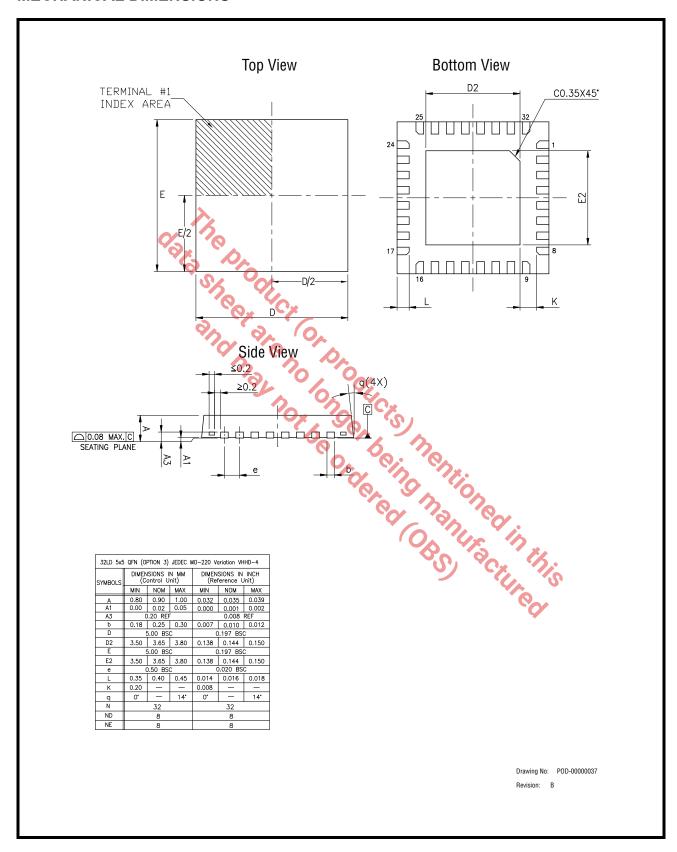

#### node, inc. enabled. The V382 is available in a 32-pin QFN package. APPLICATIONS Industrial and Embedded PCs Factory Automation and Process Controls Network Routers Roard Designs Single ... 5V tolerant inputs 32-QFN package (5mm x 5mm) GND TXA / PS\_3F8\_IRQA TXFIFO (IrDA Encoder) IRTXA# / PS\_CONF\_KEY0 Rate PCIRST# Generator RXA LCLK LPC RX FIFO IFRAMF# Bus (IrDA Decoder) IRRXA# LAD[3:01◄ Interface SERIRQ -RTSA#/PS\_CONF\_2E/RS485 Status and Control Modem IOs Registers ► DTRA#/PS\_3E0\_IRQA CTSA#, DSRA#, CDA#, RIA# Global UART Channel A Configuration Registers Baud TX FIFO ► TXB / PS\_2F8\_IRQB Watch Rate WDTOUT#/◄ Dog Generator PS WDT Timer **RX FIFO** RXB Status and ► RTSB#/PS\_CONF\_KEY1/RS485 Clock Control CLKIN Modem IOs ► DTRB#/PS\_2E0\_IRQB Divider Registers CTSB#, DSRB#, CDB#, RIB# UART Channel B

#### **FEATURES**

- 128 Byte Transmit and Receive FIFO

- Compliant to LPC 1.1 Specifications

- -40°C to +85°C Industrial Temp Operation

- Watchdog Timer with WDTOUT# signal

- 2 independent UART channels

- Programmable I/O mapped base addresses

- Data rates up to 3 Mbps

- Selectable RX FIFO interrupt trigger levels

- Auto RS-485 Half-Duplex Control mode

- Programmable character lengths (5, 6, 7, 8) with even, odd, or no parity

- IrDA mode and separate IRTXA# and IRRXA# pins for the first UART channel

- 9-bit (Multidrop) mode

- Single 3.3V Supply Voltage ( ± 10%)

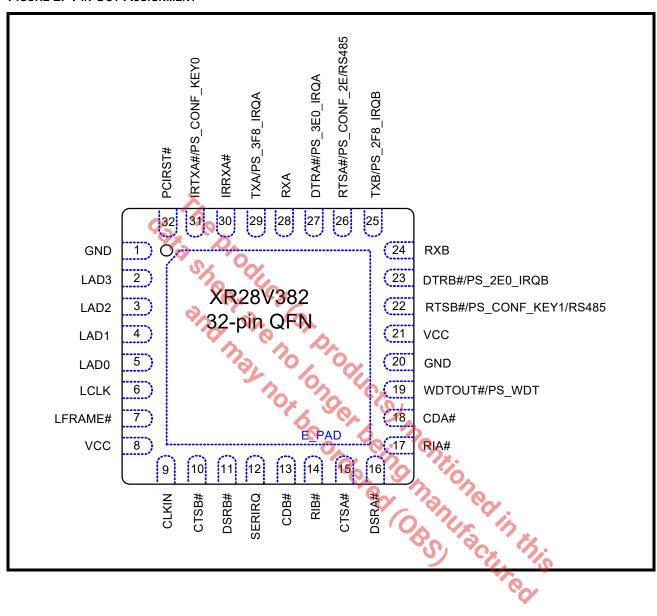

FIGURE 2. PIN OUT ASSIGNMENT

# Ordering Information<sup>(1)</sup>

| PART NUMBER        | OPERATING TEMPERATURE RANGE | LEAD-FREE          | PACKAGE       | PACKAGING METHOD |

|--------------------|-----------------------------|--------------------|---------------|------------------|

| XR28V382IL32-F     | -40°C to +85°C              | Yes <sup>(2)</sup> | 32-Lead QFN   | Tray             |

| XR28V382IL32TR-F   | 40 0 10 100 0               | 162.               | 02 Load Qi iV | Tape and Reel    |

| XR28V382IL32-0A-EB | XR28V382 Evaluation Board   |                    |               |                  |

## Notes:

- 1. Refer to www.exar.com/XR28V382 for most up-to-date Ordering Information.

- 2. Visit www.exar.com for additional information on Environmental Rating.

# **PIN DESCRIPTIONS**

# **Pin Description**

| NAME                          | 32-QFN<br>PIN#   | Түре                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LPC BUS INTERF                | ACE              | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                  |

| PCIRST#                       | 32               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Active low Reset signal.                                                                                                                                                                                                                                                                                                                                                                         |

| LAD3<br>LAD2<br>LAD1<br>LAD0  | 2<br>3<br>4<br>5 | I/O                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Multiplexed address / data bus [3:0]. See 'Section 1.2, LPC Bus Interface'.                                                                                                                                                                                                                                                                                                                      |

| LCLK                          | 6                | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | LPC clock input up to 33.3MHz.                                                                                                                                                                                                                                                                                                                                                                   |

| LFRAME#                       | 95               | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Active low LPC Frame signal indicates start of a new cycle or termination of a broken cycle.                                                                                                                                                                                                                                                                                                     |

| SERIRQ                        | 12               | The state of the s | Bi-directional pin for sending interrupts. By default this pin is tri-stated when idle. Interrupts can be active high or low. See 'Section 1.2.1, Serial IRQ' and See 'Section 2.2.1.3, Interrupt Enable Register (IER) - Read/Write' for more information regarding interrupts.                                                                                                                 |

| UART I/O INTERFA              | ACE              | 10/                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | O D                                                                                                                                                                                                                                                                                                                                                                                              |

| CTSB#                         | 10               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UART Channel B Clear-to-Send (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                  |

| DSRB#                         | 11               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel BChannel B Data-Set-Ready (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                        |

| CDB#                          | 13               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel B Carrier-Detect (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                 |

| RIB#                          | 14               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel B Ring-Indicator (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                 |

| RTSB#/PS_CON-<br>F_KEY1/RS485 | 22               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel B Request-to-Send (active low) or general purpose output or automatic RS485 Half Duplex control pin. See 'Section 1.4.4, Auto RS-485 Half-Duplex Control'.  This pin has an internal pull-up resistor and is sampled upon power-up or reset See Table 1 'UART Power On Configuration'.                                                                                              |

| DTRB#/<br>PS_2E0_IRQB         | 23               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel B Data-Terminal-Ready (active low) or general purpose output .  This pin has an internal pull-up resistor and is sampled upon power-up or reset.  This will determine the default register settings for UART channel B. The registers can later be modified by the software.  See Table 1 'UART Power On Configuration'.                                                            |

| RXB                           | 24               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel B Receive data. Normal receive data input must idle at logic 1 condition. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                               |

| TXB/<br>PS_2F8_IRQB           | 25               | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel B Transmit Data. The TXB signal will be a logic 1 during reset or idle (no data). If it is not used, leave it unconnected.  This pin has an internal pull-up resistor and is sampled upon power-up or reset. This will determine the default register settings for UART Channel B. The registers can later be modified by the software.  See Table 1 'UART Power On Configuration'. |

| CTSA#                         | 15               | I                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | UART Channel A Clear-to-Send (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                  |

# **Pin Description**

| Name                            | 32-QFN<br>PIN# | Түре | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                     |

|---------------------------------|----------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DSRA#                           | 16             | I    | UART Channel A Data-Set-Ready (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                |

| RIA#                            | 17             | I    | UART Channel A Ring-Indicator (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                |

| CDA#                            | 18             | I    | UART Channel A Carrier-Detect (active low) or general purpose input. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                                |

| RTSA# /<br>PS_CONF_2E/<br>RS485 | 26             | 0    | UART Channel A Request-to-Send (active low) or general purpose output.  This pin has an internal pull-up resistor and is sampled upon power-up or reset.  The registers can later be modified by the software. See Table 1 'UART Power On Configuration'.                                                                                                                                       |

| DTRA# /<br>PS_3E0_IRQA          | 27             | 100h | UART Channel A Data-Terminal-Ready (active low) or general purpose output.  This pin has an internal pull-up resistor and is sampled upon power-up or reset.  This will determine the default register settings for UART Channel A. The registers can later be modified by the software. See Table 1 'UART Power On Configuration'.                                                             |

| RXA                             | 28             | 10   | UART Channel A Receive data. The receive data input must idle at logic 1 condition. This input should be connected to VCC or GND when not used.                                                                                                                                                                                                                                                 |

| TXA /<br>PS_3F8_IRQA            | 29             | 0    | UART Channel A Transmit Data. The TXA signal will be a logic 1 during reset or idle (no data). If it is not used, leave it unconnected.  This pin has an internal pull-up resistor and is sampled upon power-up or reset. This will determine the default register settings for UART Channel A. The registers can later be modified by the software. See Table 1 'UART Power On Configuration'. |

| IRRXA#                          | 30             | I    | Infrared Receiver input. The infrared receive data input idles at logic 0. This input should be connected to GND when not used.                                                                                                                                                                                                                                                                 |

| IRTXA#                          | 31             | 0    | Infrared Transmitter output. The IRTXA# signal will be a logic 0 during reset or idle (no data).                                                                                                                                                                                                                                                                                                |

| ANCILLARY SIGN                  | ALS            |      | S) 80x 1/1;                                                                                                                                                                                                                                                                                                                                                                                     |

| CLKIN                           | 9              | I    | Clock input 24 MHz or 48 MHz.                                                                                                                                                                                                                                                                                                                                                                   |

| WDTOUT#/<br>PS_WDT              | 19             | 0    | Active low watchdog timer output. This pin is open drain and needs a pull-up resistor if it is used. The registers can later be modified by the software. See Table 1 'UART Power On Configuration'.                                                                                                                                                                                            |

| POWER SIGNALS                   | •              |      |                                                                                                                                                                                                                                                                                                                                                                                                 |

| VCC                             | 8, 21          | Pwr  | 3.3V ± 10% power supply.                                                                                                                                                                                                                                                                                                                                                                        |

| GND                             | 1, 20          | Pwr  | Power supply common, ground.                                                                                                                                                                                                                                                                                                                                                                    |

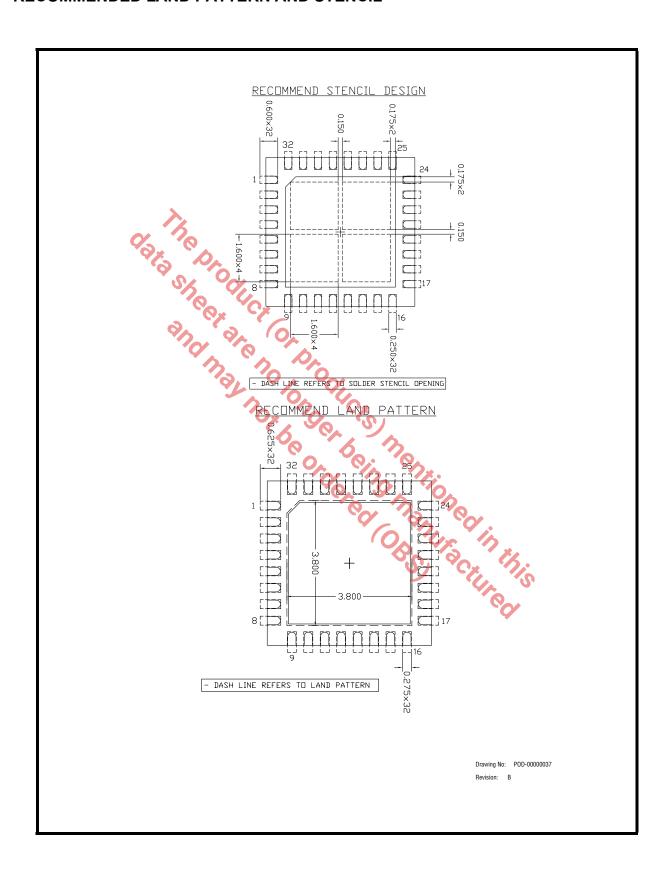

| GND                             | Center<br>Pad  | Pwr  | The center pad on the back side of the QFN package is metallic and should be connected to GND on the PCB. The thermal pad size on the PCB should be the approximate size of this center pad and should be solder mask defined. The solder mask opening should be at least 0.0025" inwards from the edge of the PCB thermal pad.                                                                 |

Pin type: I=Input, O=Output, I/O= Input/output, Pwr=Power supply.

# 1.0 FUNCTIONAL DESCRIPTIONS

# 1.1 Power on Strapping Options

At power-on, strapping options for each pin listed in Table 1 result in the register values based upon the pin state selected. These register values can also be modified by the software.

# 1.1.1 UART/Watchdog Timer Options

The V382 provides five pins for power on hardware strapping options to select the settings of the UART channels and Watchdog Timer.

**TABLE 1: UART POWER ON CONFIGURATION**

| PIN<br>NUMBER | PIN NAME             | PIN<br>STATE | ENABLE<br>(0x30) | BASE<br>ADDRESS<br>HIGH<br>REGISTER<br>(0x60) | Base<br>Address<br>Low<br>Register<br>(0x61) | IRQSEL<br>(0x70) | COMMENT                        |

|---------------|----------------------|--------------|------------------|-----------------------------------------------|----------------------------------------------|------------------|--------------------------------|

| 23            | DTRB# /              | 0,1          | 0x1              | 0x2                                           | 0xE0                                         | 0x4              |                                |

|               | PS_2E0_IRQB          | 0            | 0x0              | 0x0                                           | 0x0                                          | 0x0              | When both pins are high, the   |

| 25            | TXB /                | M            | 0x1 0            | 0x2                                           | 0xF8                                         | 0x4              | base address<br>will be 0x2F8. |

|               | PS_2F8_IRQB          | 0            | 0x0              | 0x0                                           | 0x0                                          | 0x0              | WIII DO OXZI O.                |

| 27            | DTRA# /              | 1            | 0x1              | 0x3                                           | 0xE0                                         | 0x3              | 144                            |

|               | PS_3E0_IRQA          | 0            | 0x0              | 0x0                                           | 0x0                                          | 0x0              | When both pins are high, the   |

| 29            | TXA /<br>PS_3F8_IRQA | 1            | 0x1              | 0x3                                           | 0xF8                                         | 0x3              | base address<br>will be 0x3F8. |

|               | F3_3F6_INQA          | 0            | 0x0              | 0x0                                           | 0x0                                          | 0x0              |                                |

| 19            | WDTOUT# /            | 1            | 0x1              | 0x4                                           | 0x42                                         | 0x0              |                                |

|               | PS_WDT               | 0            | 0x0              | 0x0                                           | 0x0                                          | 0x0              |                                |

After power-on, the Enable, Base Address High & Low, IRQSEL registers can be modified by the software.

# 1.1.2 Configuration Port and Key Selection Options

# 1.1.2.1 Configuration Port Selection Option

The configuration registers are programmed by the index port and the data port. The port address is determined by the strap pin RTSA#/PS\_CONF\_2E/RS485. If an external pull-down resistor is not installed, the default value of the RTSA#/PS\_CONF\_2E/RS485 pin is '1' when the system powers on. Therefore, the default index port address is 0x2E and the data port address is 0x2F.

**TABLE 2: CONFIGURATION PORT SELECTION**

| RTSA#/PS_CONF_2E/RS485 (Pin 26) | INDEX PORT ADDRESS | DATA PORT ADDRESS |  |

|---------------------------------|--------------------|-------------------|--|

| 0                               | 0x4E               | 0x4F              |  |

| 1 (default)                     | 0x2E               | 0x2F              |  |

# 1.1.2.2 Configuration Entry Key Options

In order to enable the configuration register access mode, the entry key needs to be written consecutively twice to the index port. The entry key is generated by the power on setting pins RTSB#/PS\_CONF\_KEY1/RS485 and IRTXA#/PS\_CONF\_KEY0.

**TABLE 3: CONFIGURATION ENTRY KEY**

| RTSB#/PS_CONF_KEY1/RS485<br>(PIN 22) | IRTXA#/PS_CONF_KEY0<br>(Pin 31) | ENTRY KEY      |

|--------------------------------------|---------------------------------|----------------|

| 0                                    | 0                               | 0x77           |

| 0                                    | 1                               | 0xA0           |

| 1                                    | 0                               | 0x87           |

| 1 %                                  | 1                               | 0x67 (Default) |

In order to disable the configuration register access mode, 0xAA must be written to the index port.

# 1.1.2.3 Example

# 1.1.2.3.1 Index port address 0x2E & Data port address 0x2F (default)

```

write (0x2E, 0x67);

//write entry key (0x67) twice to configuration port

write (0x2E, 0x67);

//Enable access to the configuration registers

write (0x2E, 0x20);

//Select the DEV_ID_M register

//Read the DEV ID M register

read (0x2F);

write (0x2E, 0x21);

//Select the DEV ID L register

//Read the DEV ID L register

read (0x2F);

//Select the Clock Select Registe

write (0x2E, 0x25);

write (0x2F, 0x1);

//Select the input clock frequency 48

write (0x2E, 0x7);

//Select the LDN register

write (0x2F, 0x1);

//Select the UART Channel B

//Select the FIFO Mode Select Register of UART Channel B

write (0x2E, 0xF6);

write (0x2F, 0x3);

//Set the FIFO size 128 bytes,

//RX trigger level 1, 4, 8, 14 and no delay for THR empty interrupt

write (0x2E, 0x30);

//Enable the UART Channel B

write (0x2F, 0x1);

write (0x2E, 0xAA);

//Disable access to configuration registers

```

#### 1.1.2.3.2 Index port address 0x4E & Data port address 0x4F

```

write (0x4E, 0x67);

write (0x4E, 0x67);

//write entry key (0x67) twice to configuration port

//Enable access to the configuration registers

write (0x4E, 0x23);

//Select the VID M register

read (0x4F);

//Read the VID_M register

write (0x4E, 0x24);

//Select the VID_L register

read (0x4F);

//Read the VID_L register

write (0x4E, 0x25);

//Select the Clock Select Register

write (0x4F, 0x0);

//Select the input clock frequency 24 MHz

write (0x4E, 0x7)

//Select the LDN register

write (0x4F, 0x0)

//Select the UART Channel A

write (0x4E, 0x60)

#Set the UART Channel A base address high byte as 0x3

write (0x4F, 0x3);

write (0x4E, 0x61);

write (0x4F, 0xF8);

//Set the UART Channel A base address low byte as 0xF8

//Select the FIFO Mode Select Register of UART Channel A

write (0x4E, 0xF6);

//Set the FIFO size 16 bytes,

write (0x4F, 0x0);

//RX trigger level 1, 4, 8, 14 and no delay for THR empty interrupt

write (0x4E, 0x30);

//Enable the UART Channel

write (0x4F, 0x1);

write (0x4E, 0xAA);

//Disable access to the configuration registers

```

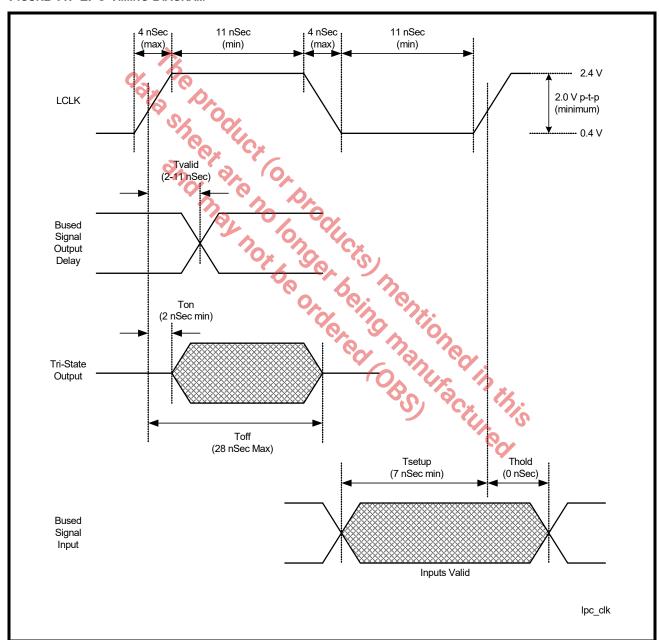

#### 1.2 LPC Bus Interface

The LPC bus interface has a 4-bit multiplexed address/data bus, 1 reset signal, 1 clock and 1 control signal. It also has one interrupt signal. The V382 implements the following signals of the LPC bus.

- LFRAME# is used by the host to start or stop transfers.

- LCLK is a clock used for synchronization.

- PCIRST# is an active low reset signal.

- LAD[3:0] signal lines communicate device address, control (read, write, wait and transfer type), and data information over the LPC bus between a host and a peripheral.

- Interrupt requests are issued through SERIRQ.

#### 1.2.1 Serial IRQ

The V382 supports a serial IRQ scheme specified in specification for Serialized IRQ support for PCI system Rev6.0 which allows SERIRQ pin to be shared with multiple devices. The SERIRQ signal is tri-stated when idle. The SERIRQ is divided into 3 types of time slots known as Frames; Start frame, IRQ frame, and Stop frame. The SERIRQ uses LCLK for timing. There are two modes of operation for SERIRQ signal: Quiet mode and Continuous mode. These two modes are discussed in further detail in 'Section 1.2.1.1, Start Frame'.

#### 1.2.1.1 Start Frame

The Start frame indicates begining of the SERIRQ cycle. During this frame the SERIRQ is driven LOW for 4-8 clock cycles. It can be initiated by the host or V382 depending on the mode of operation.

In the Continuous mode, only the host controller initiates the Start frame to update the SERIRQ line information. The host controller drives the SERIRQ signal low for 4 to 8 clock periods. Upon a reset, the SERIRQ signal defaults to the Continuous mode for the host controller to initiate the first Start frame.

In the Quiet mode, the Start frame is initiated by the device/host. The V382 drives the SERIRQ signal active low for one clock to initiate a Start Frame, and then tri-states it immediately. The host controller will then take over driving SERIRQ signal low in the next clock and will continue driving the SERIRQ low for 3 to 7 clock periods. This makes the total number of clocks low for 4 to 8 clock periods. After these clocks, the host controller will drive the SERIRQ high for one clock and then tri-states it.

A Start Frame may not be initiated while SERIRQ is active. The SERIRQ is active between Start and Stop frames while it is idle between Stop and Start frames.

#### IRQ Frame 1.2.1.2

Once the start frame has been initiated, all the peripherals must start counting frames based on the rising edge of the clock (LCLK). Each IRQ Frame is three clocks: Sample phase, Recovery phase, and Turn-around phase. During the Sample phase, the peripheral drives SERIRQ low if the corresponding IRQ is active. If the corresponding IRQ is inactive, then SERIRQ will be left tri-stated. During the Recovery phase, the peripheral device drives the SERIRQ high During the Turn-around phase, the peripheral device leaves the SERIRQ tristated. The V382 supports IRQ3, IRQ4, IRQ5, IRQ7, IRQ9, IRQ10, and IRQ11.

TABLE 4: SERIRQ SAMPLING PERIODS

| IRQ/DATA FRAME | SIGNAL SAMPLED | NUMBER OF CLOCKS PAST START |

|----------------|----------------|-----------------------------|

| 1              | IRQ0           | 2                           |

| 2              | JRQ1           | 5                           |

| 3              | SMI#           | 8                           |

| 4              | IRQ3           | 11                          |

| 5              | IRQ4           | 14                          |

| 6              | IRQ5           | 17                          |

| 7              | IRQ6           | <b>4</b> 20                 |

| 8              | IRQ7           | 23                          |

| 9              | IRQ8           | 26                          |

| 10             | IRQ9           | 29                          |

| 11             | IRQ10          | 32                          |

| 12             | IRQ11          | 35                          |

| 13             | IRQ12          | 38                          |

| 14             | IRQ13          | 41                          |

| 15             | IRQ14          | 44                          |

| 16             | IRQ15          | 47                          |

| 17             | IOCHCK#        | 50                          |

| 18             | INTA#          | 53                          |

| 19             | INTB#          | 56                          |

| 20             | INTC#          | 59                          |

| 21             | INTD#          | 62                          |

| 32:22          | Unassigned     | 95                          |

## 1.2.1.3 Stop Frame

After all IRQ/Data Frames have been completed, the host controller will terminate SERIRQ by a Stop frame. Only the host controller can initiate the Stop frame by driving SERIRQ low for 2 or 3 clocks. If the Stop Frame is low for 2 clocks, the next SERIRQ cycle will be the Quiet mode whereas if it is low for 3 clocks, the next SERIRQ cycle will be the Continuous mode.

## 1.3 Watchdog Timer (WDT)

The WDT is typically used in a system to initiate any of the several types of corrective action, including processor reset, power cycling, fail-safe activation etc. The Watchdog timer of V382 is an 8 bit counter controlled by six registers. See 'Section 2.1.2.2, Watchdog Timer Registers (LDN = 0x08)' WDTOUT#/PS\_WDT idles HIGH and will transition LOW when a time out occurs. The V382 provides three time intervals: 10 ms, 1s and 1 minute allowing for timeouts ranging from approximately 2.5 seconds to more than 4 hours. See'Section2.1.2.2.4, WDTTimerStatusandControlRegister-Read/Write'tosetuptimeinterval.

#### 1.4 **UART**

# 1.4.1 External Clock Input (CLKIN)

Along with LCLK, the V382 also needs an external clock for UART data communication. It can support any clock up to 48MHz. The 24MHz and 48MHz are the standard clock frequencies supported by the V382. See 'Section 2.1.1.5, Clock Select Register - Read/Write'.

# 1.4.1.1 Programmable Baud Rate Generator

Each UART has its own Baud Rate Generator (BRG) with a prescaler. The prescaler is controlled by Bit[1:0] of Enhanced Multifunction Register - Read/Write

Table 5 shows the standard data rates available with a 24 MHz external clock at 16X sampling rate and internal clock frequency set to 1.8462 MHz. The divisor value can be calculated for DLL/DLM with the following equation.

divisor (decimal) = (Internal clock frequency) / (serial data rate x 16)

Table 8 lists the different internal clock settings.

TABLE 5: TYPICAL DATA RATES WITH A 1.8462MHZ INTERNAL CLOCK

| BAUD Rate<br>(BPS) | DIVISOR FOR 16x<br>Clock (Decimal) | Divisor for 16x<br>Clock (HEX) | DLM<br>PROGRAM<br>VALUE (HEX) | DLL<br>PROGRAM<br>VALUE (HEX) | ACTUAL<br>BAUD RATE | DATA RATE<br>ERROR (%) |

|--------------------|------------------------------------|--------------------------------|-------------------------------|-------------------------------|---------------------|------------------------|

| 300                | 384                                | 180                            | 01                            | 80                            | 300.48              | 0.2                    |

| 600                | 192                                | C0                             | 00                            | C0                            | 600.96              | 0.2                    |

| 1200               | 96                                 | 60                             | 00                            | 60                            | 1201.92             | 0.2                    |

| 2400               | 48                                 | 30                             | 00                            | 30                            | 2403.85             | 0.2                    |

| 4800               | 24                                 | 18                             | 00                            | 18                            | 4807.69             | 0.2                    |

| 9600               | 12                                 | 0C                             | 00                            | 0C                            | 9615.39             | 0.2                    |

| 19200              | 6                                  | 06                             | 00                            | 06                            | 19230.77            | 0.2                    |

| 38400              | 3                                  | 03                             | 00                            | 03                            | 38461.54            | 0.2                    |

| 57600              | 2                                  | 02                             | 00                            | 02                            | 57692.31            | 0.2                    |

| 115200             | 1                                  | 01                             | 00                            | 01                            | 115384.6            | 0.2                    |

#### 1.4.2 Transmitter

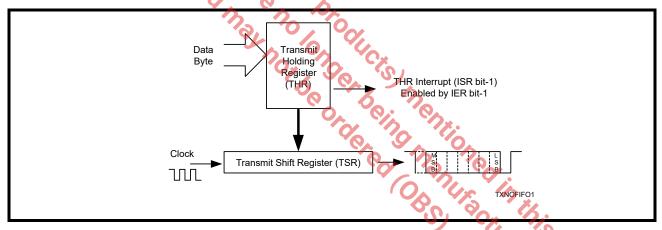

The transmitter section comprises of an 8-bit Transmit Shift Register (TSR) and up to 128 bytes of FIFO which includes a byte-wide Transmit Holding Register (THR). TSR shifts out every data bit with the internal sampling clock. The transmitter sends the start bit followed by the number of data bits, inserts the proper parity bit if enabled, and adds the stop bit(s). The status of the THR and TSR are reported in the Line Status Register (LSR bit-5 and bit-6).

# 1.4.2.1 Transmit Holding Register (THR) - Write Only

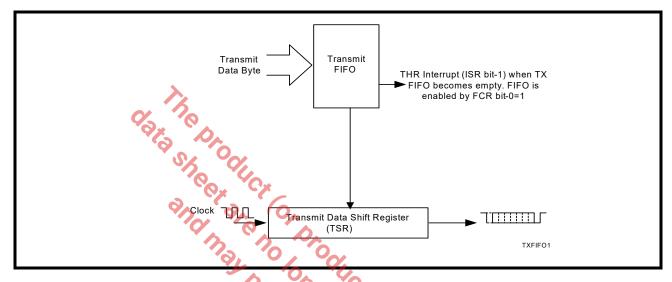

The transmit holding register is an 8-bit register providing a data interface to the host processor. The host writes transmit data byte to the THR to be converted into a serial data stream including start bit, data bits, parity bit and stop bit(s). The least significant bit (Bit-0) becomes first data bit to go out. The THR is the input register to the transmit FIFO of up to 128 bytes when FIFO operation is enabled by FCR bit-0. Every time a write operation is made to the THR, the FIFO data pointer is automatically bumped to the next sequential data location.

# 1.4.2.2 Transmitter Operation in non-FIFO Mode

The host loads transmit data to THR one character at a time. The THR empty flag (LSR bit-5) is set when the data byte is transferred to TSR. THR flag can generate a transmit empty interrupt (ISR bit-1) when it is enabled by IER bit-1. The TSR flag (LSR bit-6) is set when TSR becomes completely empty.

FIGURE 3. TRANSMITTER OPERATION IN NON-FIFO MODE

#### Transmitter Operation in FIFO Mode 1.4.2.3

The host may fill the transmit FIFO with up to 128 bytes of transmit data. The THR empty flag (LSR bit-5) is set whenever the FIFO is empty. The THR empty flag can generate a transmit empty interrupt (ISR bit-1) when the FIFO becomes empty. The transmit empty interrupt is enabled by IER bit-1. The TSR flag (LSR bit-6) is set when TSR/FIFO becomes empty.

FIGURE 4. TRANSMITTER OPERATION IN FIFO MODE

#### 1.4.3 Receiver

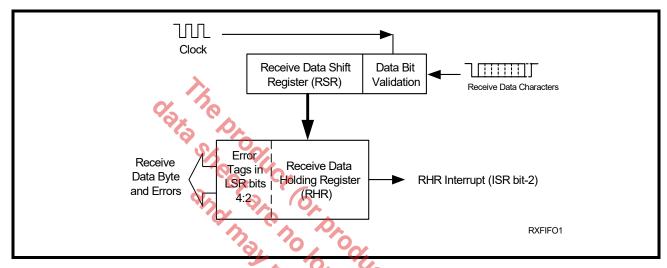

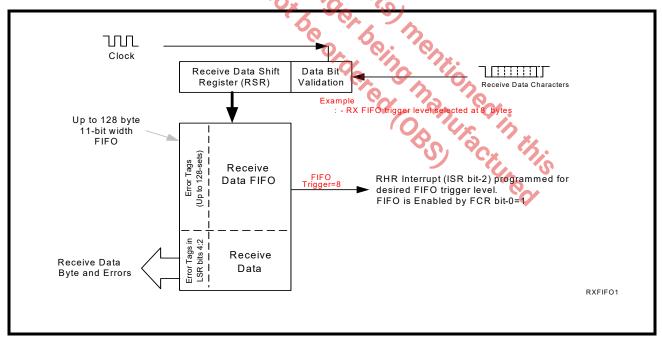

The receiver section contains an 8-bit Receive Shift Register (RSR) and up to 128 bytes of FIFO which includes a byte-wide Receive Holding Register (RHR). The RSR uses the internal sampling clock for timing. It verifies and validates every bit on the incoming character in the middle of each data bit. On the falling edge of a start or false start bit, an internal receiver counter starts counting at the clock rate. After 8 clocks the start bit period should be at the center of the start bit. At this time the start bit is sampled and if it is still a logic 0 it is validated. Evaluating the start bit in this manner prevents the receiver from assembling a false character. The rest of the data bits and stop bits are sampled and validated in this same manner to prevent false framing. If there were any error(s), they are reported in the LSR register bits 2-4. Upon unloading the receive data byte from RHR, the receive FIFO pointer is bumped and the error tags are immediately updated to reflect the status of the data byte in RHR register. RHR can generate a receive data ready interrupt upon receiving a character or delay until it reaches the FIFO trigger level. Furthermore, data delivery to the host is guaranteed by a receive data ready time-out interrupt when data is not received for 4 word lengths as defined by LCR[1:0] plus 12 bits time. This is equivalent to 3.7-4.6 character times. The RHR interrupt is enabled by IER bit-0. See Figure 5.

# 1.4.3.1 Receive Holding Register (RHR) - Read-Only

The Receive Holding Register is an 8-bit register that holds a receive data byte from the Receive Shift Register. It provides the receive data interface to the host processor. The RHR register is part of the receive FIFO of up to 128 bytes by 11-bits wide, the 3 extra bits are for the 3 error tags to be reported in LSR register. When the FIFO is enabled by FCR bit-0, the RHR contains the first data character received by the FIFO. After the RHR is read, the next character byte is loaded into the RHR and the errors associated with the current data byte are immediately updated in the LSR bits 2-4.

FIGURE 5. RECEIVER OPERATION IN NON-FIFO MODE

FIGURE 6. RECEIVER OPERATION IN FIFO MODE

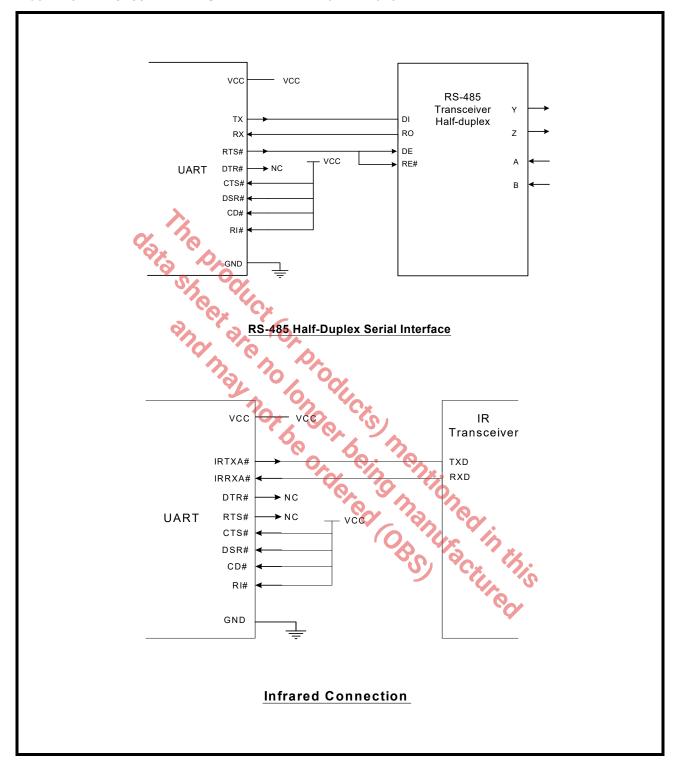

# 1.4.4 Auto RS-485 Half-Duplex Control

The Auto RS-485 Half-Duplex Control feature changes the behavior of the RTS#/RS485 pin when enabled by **Enhanced Multifunction Register - Read/Write** bit-4. If enabled, by default, it de-asserts RTS#/RS485 ouput following the last stop bit of the last character that has been transmitted. This helps in turning around the transceiver to receive the remote station's response. When the host is ready to transmit data packet, it only has to load data bytes to the transmit FIFO. The transmitter automatically asserts RTS#/RS485 output prior to sending the data. The polarity of RTS#/RS485 signal can be modified by bit-5 of Enhanced Multifunction register.

## 1.4.5 Normal Multidrop (9-bit) Mode

Normal multidrop mode is enabled when bit-7 of Enhanced Multifunction register in the UART Device Configuration Registers is set to '1'. In the multidrop (9-bit) mode, the parity bit becomes the address/data bit.

If a data byte is received (9th bit is '0'), it will be loaded into the RX FIFO and the parity error bit will be '0'. If an address byte is received (9th bit is '1'), it will be loaded into the RX FIFO and the parity error bit will be '1'. When the address byte has been received, the software will need to examine the byte: If the address matches its slave address, the receiver will receive the subsequent data; If the address does not match its slave address, then the receiver will discard the data.

# 1.4.5.1 Auto Address Detection

Auto Address Detection mode is enabled when bit-6 of Enhanced Multifunction register (0xF0) in UART device configuration registers set is set to '1'. The desired slave address will need to be written into the 9-bit mode slave address register (0xF4) in the UART device configuration registers set. If the received byte is an address byte that does not match the programmed character in the 9-bit mode slave address register, the receiver will discard these data. Upon receiving an address byte that matches the 9-bit mode slave address register character, the receiver will automatically push the address byte into the RX FIFO and set the parity error bit in the LSR register. The receiver also generates an LSR interrupt if enabled. The receiver will then receive the subsequent data. If another address byte is received and does not match the programmed 9-bit mode slave address register value, then the receiver will ignore the data that follows.

#### 1.4.6 Infrared Mode

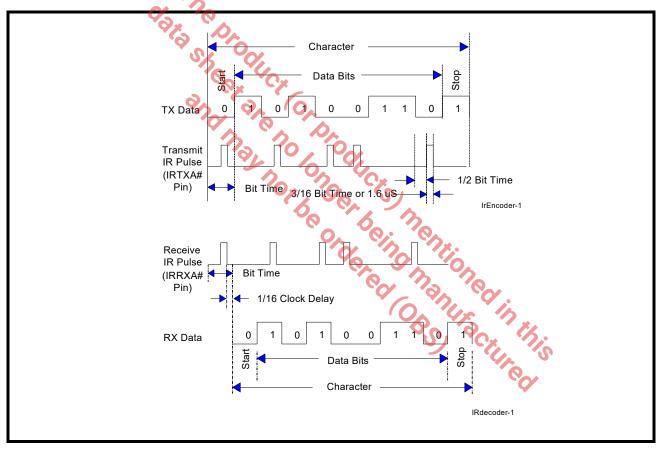

The V382 UART Channel A includes the infrared encoder and decoder compatible to IrDA (Infrared Data Association) version 1.0. The infrared encoder sends out a 3/16 of a bit wide or 1.6 uS HIGH pulse for each "0" bit in the transmit data stream with a data rate up to 115.2 kbps. This signal encoding reduces the on-time of the infrared LED, hence reduces the power consumption. See Figure 7.

The infrared encoder and decoder are enabled by setting Infrared Mode Control Register - Read/Write bit-4 to a '1'. The IRRXA# input assumes an idle level of logic zero after a reset and power up, see Figure 7. The IRRXA# input will assume an idle level of logic HIGH if bit-0 of the Infrared Mode Control Register - Read/Write is set to '1'. The IRTXA# is idle at LOW by default. The IRTXA# will be idle at HIGH if bit-1 of the Infrared Mode Control Register - Read/Write is set to '1'.

Typically, the wireless infrared decoder receives the input pulse from the infrared sensing diode on the IRRXA# pin. Each time it senses a light pulse, it returns a logic 0 to the data bit stream.

FIGURE 7. INFRARED TRANSMIT DATA ENCODING AND RECEIVE DATA DECODING

## 1.4.7 Internal Loopback