### XR81112

# Universal Clock - High Frequency LVCMOS/LVDS/LVPECL Clock Synthesizer

#### **General Description**

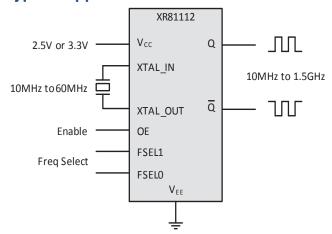

The XR81112 is a family of Universal Clock synthesizer devices in a compact QFN-12 package. The devices generate ANY frequency in the range of 10 MHz to 1.5GHz by utilizing a highly flexible delta sigma modulator and a wide ranging VCO. The outputs are configurable for single ended LVCMOS or differential LVDS or LVPECL. The clock outputs have very low phase noise jitter of sub 0.6ps while consuming extremely low power. These devices can be used with standard crystals or an external system clock and can be configured to select from four different frequency multiplier settings to support a wide variety of applications. This family of products have an extremely low power PLL block with core power consumption less than 40% of equivalent devices in the market.

The XR81112 is a clock synthesizer with Integer/fractional divider, LVCMOS/LVDS/LVPECL driver, 3.3V/2.5V supply, taking a Xtal input and providing one of four selectable output frequencies. The device is optimized for use with a fundamental mode 10MHz to 60MHz crystal (or system clock) and generates a selection of output frequencies from 10MHz to 1.5GHz in either integer or fractional mode. In fractional mode, frequency resolution of less than 1Hz steps can be achieved.

The application diagram below shows a typical synthesizer configuration with any standard crystal oscillating in fundamental mode. Internal load capacitors are optionally available to minimize/eliminate external crystal loads. A system clock can also be used to overdrive the oscillator for a synchronous timing system.

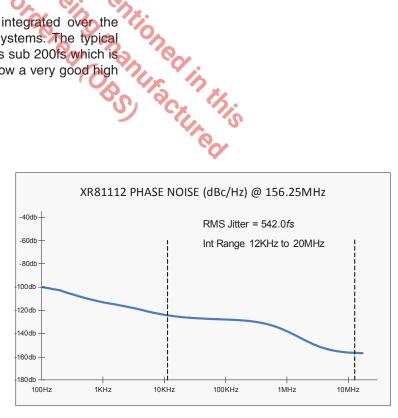

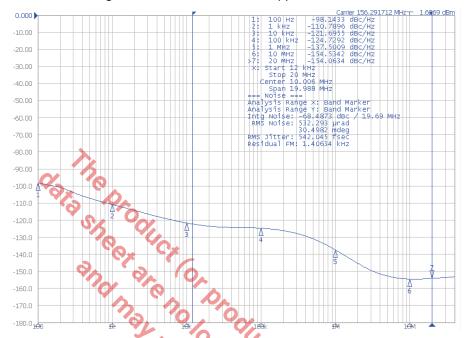

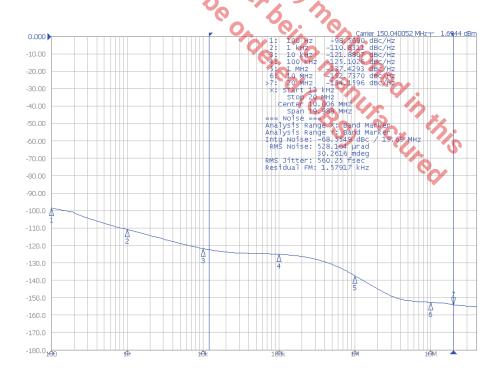

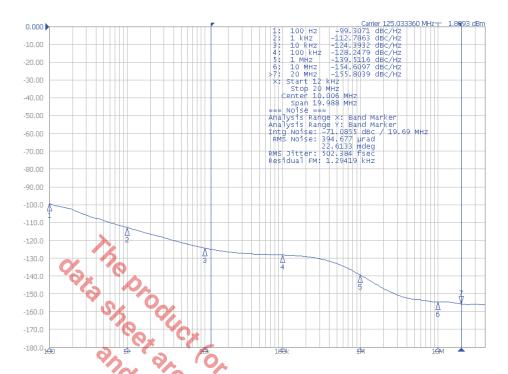

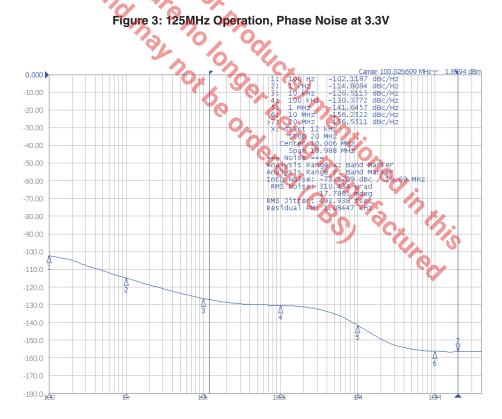

The typical phase noise plot below shows the jitter integrated over the 12KHz to 20MHz range that is widely used in WAN systems. The typical noise for the integration range of 1.875MHz to 20MHz is sub 200fs which is important for LAN applications. These clock devices show a very good high frequency noise floor below -150dB.

#### **FEATURES**

- Small footprint 3mm x 3mm QFN package

- Configurable As one differential LVPECL/LVDS output pair or as a single ended LVCMOS output

- Crystal oscillator interface which can also be overdriven using a single-ended reference clock

- Output frequency range: 10MHz 1500MHz

- Crystal/input frequency: 10MHz to 60MHz, parallel resonant crystal

- VCO range: 2GHz 3GHz

- RMS phase jitter @ 156.25MHz, 12KHz 20MHz: <0.60ps</li>

- Full 3.3V or 2.5V operating supply

- -40°C to 85°C ambient operating temperature

- Lead-free (RoHS 6) package

#### **APPLICATIONS**

- 10GE, GE LAN/WAN

- 2.5G/10G SONET/SDH/OTN

- xDSL, PCIe

- Low-jitter Clock Generation

- · Synchronized clock systems

Ordering Information - back page

#### **Typical Application**

#### **Absolute Maximum Ratings**

Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Maximum Rating condition for extended periods may affect device reliability and lifetime.

| Power Supply Voltage (VCC)+4.2V                 |

|-------------------------------------------------|

| Input Voltage0.5V to VCC + 0.5V                 |

| Output Voltage0.5V to VCC + 0.5V                |

| Reference Frequency/Input Crystal10MHz to 60MHz |

| Storage Temperature55°C to +125°C               |

| Lead Temperature (Soldering, 10 sec)300°C       |

| ESD Rating (HBM - Human Body Model)2.0kV        |

#### **Operating Conditions**

Operating Temperature Range.....-40°C to +85°C

#### **Electrical Characteristics**

Unless otherwise noted:  $T_A = -40^{\circ}C$  to  $+85^{\circ}C$ ,  $V_{CC} = 3.3V \pm 5\%$  or  $2.5V \pm 5\%$ ,  $V_{EE} = 0V$

| Symbol                                                                  | Parameter                                  | Conditions                                                                                  | *  | Min                   | Тур            | Max                   | Units          |

|-------------------------------------------------------------------------|--------------------------------------------|---------------------------------------------------------------------------------------------|----|-----------------------|----------------|-----------------------|----------------|

| 3.3V Power Supply DC Characteristics                                    |                                            |                                                                                             |    |                       |                |                       |                |

| V <sub>CC</sub>                                                         | Power Supply Voltage                       |                                                                                             | •  | 3.135                 | 3.3            | 3.465                 | V              |

| lee                                                                     | Power Supply Current PECL LVDS CMOS        | Includes output loading<br>Measured at 1500MHz<br>Measured at 1500MHz<br>Measured at 200MHz | •  |                       | 86<br>34<br>48 | 120<br>50<br>65       | mA<br>mA<br>mA |

| 2.5V Powe                                                               | r Supply DC Characteristics                |                                                                                             |    |                       |                |                       |                |

| V <sub>CC</sub>                                                         | Power Supply Voltage                       |                                                                                             | •  | 2.375                 | 2.5            | 2.625                 | V              |

| lee                                                                     | Power Supply Current PECL LVDS CMOS        | Includes output loading<br>Measured at 1500MHz<br>Measured at 1500MHz<br>Measured at 200MHz | •  |                       | 69<br>25<br>37 | 95<br>35<br>50        | mA<br>mA<br>mA |

| LVCMOS/L                                                                | VTTL DC Input Characteristics              |                                                                                             |    |                       |                |                       |                |

| V <sub>IH</sub>                                                         | Input High Voltage (OE, FSEL[1:0])         | V <sub>CC</sub> = 3.465V                                                                    | •  | 2.42                  |                | V <sub>CC</sub> + 0.3 | V              |

|                                                                         |                                            | V <sub>CC</sub> = 2.625V                                                                    | •  | 1.83                  |                | V <sub>CC</sub> + 0.3 | V              |

| V <sub>IL</sub>                                                         | Input Low Voltage(OE, FSEL[1:0])           | V <sub>CC</sub> ≠3.465V                                                                     | •  | -0.3                  |                | 1.03                  | V              |

|                                                                         |                                            | V <sub>CC</sub> = 2.625V                                                                    | •  | -0.3                  |                | 0.785                 | V              |

| I <sub>IH</sub>                                                         | Input High Current (OE, FSEL[1:0])         | V <sub>IN</sub> = V <sub>CC</sub> = 3.465V or 2.625V                                        | •  |                       |                | 15                    | μΑ             |

| I <sub>IL</sub>                                                         | Input Low Current (OE, FSEL[1:0])          | V <sub>IN</sub> = 0V, V <sub>CC</sub> = 3.465V or 2.625V                                    | 7  | -10                   |                |                       | μΑ             |

| LVCMOS E                                                                | OC Output Characteristics (Vcc = 3.3 +/- 5 | 5% or Vcc = 2.5 +/- 5%)                                                                     |    | 20                    | •              |                       |                |

| V <sub>OH</sub>                                                         | Output High Voltage                        | Output Unloaded                                                                             | 7/ | 0.8 * V <sub>CC</sub> |                |                       | V              |

| V <sub>OL</sub>                                                         | Output Low Voltage                         | Output Unloaded                                                                             | ×  | 30 1                  |                | 0.1 * V <sub>CC</sub> | V              |

| LVPECL DC Output Characteristics (Vcc = 3.3 +/- 5% or Vcc = 2.5 +/- 5%) |                                            |                                                                                             |    |                       |                |                       |                |

| V <sub>OH</sub>                                                         | Output High Voltage                        |                                                                                             | •  | V <sub>CC</sub> - 1.3 |                | V <sub>CC</sub> - 0.4 | V              |

| V <sub>OL</sub>                                                         | Output Low Voltage                         |                                                                                             | •  | V <sub>CC</sub> - 2.0 |                | V <sub>CC</sub> - 1.6 | V              |

| V <sub>SWING</sub>                                                      | Peak-to-Peak Output Voltage Swing          |                                                                                             | •  | 0.6                   |                | 1.2                   | V              |

| LVDS DC Output Characteristics (Vcc = 3.3 +/- 5% or Vcc =2.5 +/- 5%)    |                                            |                                                                                             |    |                       |                |                       |                |

| V <sub>OD</sub>                                                         | Differential Output Voltage                | Output < 1GHz                                                                               | •  | 200                   |                | 550                   | mV             |

| V <sub>OC</sub>                                                         | Common Mode Voltage                        |                                                                                             | •  |                       | 1.25           |                       | V              |

| Symbol                                | Parameter                                   | Conditions                                                                                                                                      | *       | Min         | Тур | Max  | Units |

|---------------------------------------|---------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|-----|------|-------|

| Crystal Ch                            | aracteristics                               |                                                                                                                                                 |         |             |     |      |       |

| X <sub>Mode</sub>                     | Mode of Oscillations                        |                                                                                                                                                 |         | Fundamental |     |      |       |

| X <sub>f</sub>                        | Frequency                                   |                                                                                                                                                 |         | 10          |     | 60   | MHz   |

| ESR                                   | Equivalent Series Resistance                |                                                                                                                                                 |         |             |     | 50   | Ω     |

| C <sub>S</sub>                        | Shunt Capacitance                           |                                                                                                                                                 |         |             |     | 7    | pF    |

| AC Charac                             | teristics                                   |                                                                                                                                                 |         |             |     |      | 1     |

| f <sub>OUT</sub>                      | Output Frequency                            |                                                                                                                                                 |         | 10          |     | 1500 | MHz   |

| t <sub>jit</sub> (φ)                  | RMS Phase Jitter                            | 156.25MHz (w/25MHz ref)<br>Integration Range 12kHz-20MHz                                                                                        |         |             | 0.6 |      | pS    |

| t <sub>jit</sub> (φ) RMS Phase Jitter | data b                                      | 150MHz (w/25MHz ref)<br>Integration Range 12kHz-20MHz                                                                                           |         |             | 0.6 |      | pS    |

|                                       | She                                         | 125MHz (w/25MHz ref)<br>Integration Range 12kHz-20MHz                                                                                           |         |             | 0.6 |      | pS    |

|                                       | an.                                         | 100MHz (w/25MHz ref)<br>Integration Range 12kHz-20MHz                                                                                           |         |             | 0.6 |      | pS    |

| t <sub>jit</sub> (φ)Ι                 | Integer RMS Phase Jitter                    | Op Dr                                                                                                                                           | •       |             |     | 1.0  | pS    |

| t <sub>jit</sub> (φ)F                 | Fractional RMS Phase Jitter                 | with Ref input >25MHz                                                                                                                           | •       |             |     | 1.5  | pS    |

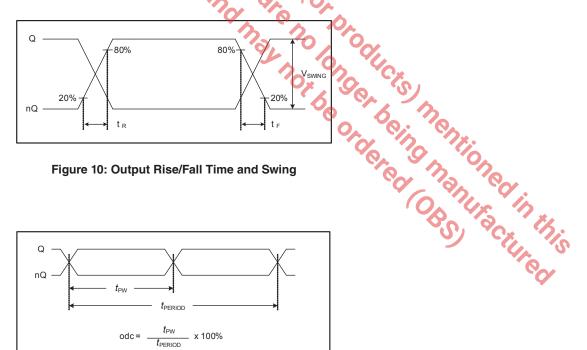

| t <sub>R</sub> /t <sub>F</sub>        | Output Rise/Fall Time                       | 20% to 80%, see Figure 10                                                                                                                       | •       | 100         |     | 500  | pS    |

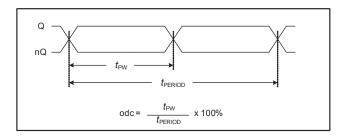

| Odc                                   | Output Duty Cycle                           | see Figure 11                                                                                                                                   | •       | 45          |     | 55   | %     |

| Limits appl                           | ying over the full operating temperature ra | 100MHz (w/25MHz ref) Integration Range 12kHz-20MHz  with Ref input >25MHz  20% to 80%, see Figure 10  see Figure 11  ange are denoted by a "•". | Anul S) | ned in the  | Š.  |      |       |

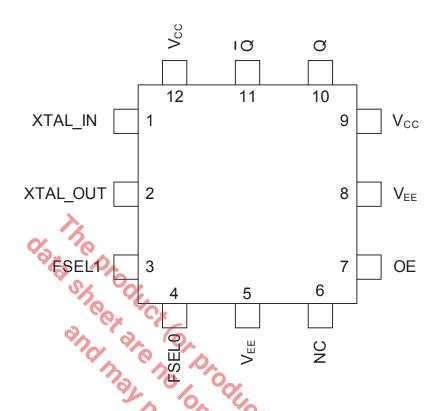

#### **Pin Configuration**

#### **Pin Assignments**

| Pin No. | Pin Name        | Туре                      | Description                                                                                                                 |

|---------|-----------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------|

| 1       | XTAL_IN         | Input                     | Crystal oscillator input.                                                                                                   |

| 2       | XTAL_OUT        | Output                    | Crystal oscillator output.                                                                                                  |

| 3       | FSEL1           | Input<br>(900KΩ pull-dwn) | Output frequency select pin, MSB (LVCMOS/LVTTL input)                                                                       |

| 4       | FSEL0           | Input<br>(900KΩ pull-dwn) | Output frequency select pin, LSB (LVCMOS/LVTTL input).                                                                      |

| 5       | V <sub>EE</sub> | Supply                    | Negative supply pin.                                                                                                        |

| 6       | NC              | No Connect                | Unused, do not connect.                                                                                                     |

| 7       | OE              | Input<br>(900KΩ pull-up)  | Output enable pin - LVCMOS/LVTTL active high input. Outputs are enabled when OE = high. Outputs are disabled when OE = low. |

| 8       | V <sub>EE</sub> | Supply                    | Negative supply pin.                                                                                                        |

| 9       | V <sub>CC</sub> | Supply                    | Power supply pin.                                                                                                           |

| 10      | Q               | Output                    | Positive output.                                                                                                            |

| 11      | Q               | Output                    | Inverted output.                                                                                                            |

| 12      | V <sub>CC</sub> | Supply                    | Power supply pin.                                                                                                           |

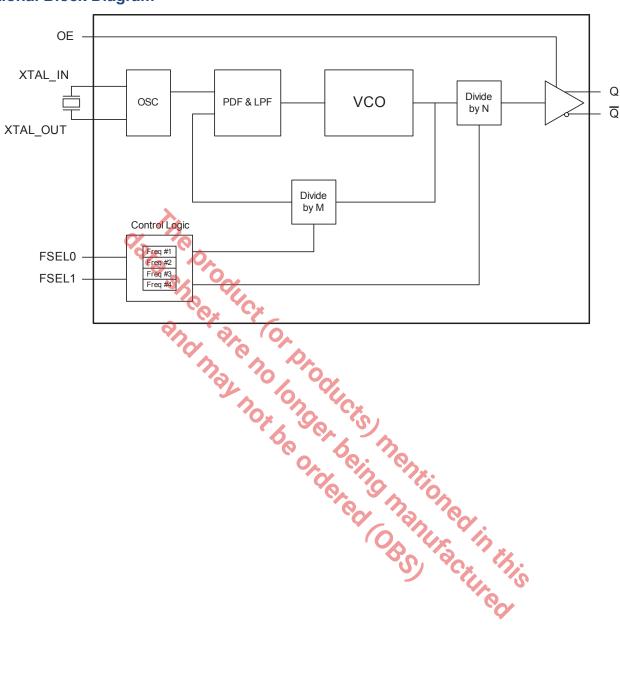

#### **Functional Block Diagram**

#### **Typical Performance Characteristics**

Figures 1, 2, 3 and 4 show typical phase noise performance plots for 156.25 MHz, 150MHz, 125M, and 100MHz clock outputs respectively. The data was taken using the industry standard Agilent E5052B instrument. The integration range is the widely referenced 12KHz to 20MHz range most often used in WAN applications.

Figure 1: 156.25MHz Operation, Phase Noise at 3.3V

Figure 2: 150MHz Operation, Phase Noise at 3.3V)

Figure 4: 100MHz Operation, Phase Noise at 3.3V

#### **Application Information**

#### **Functional Truth Table**

The XR81112 Universal Clock can support up to 4 individual output frequency configurations. Once configured, the two frequency select pins, FSLEL[1:0], will determine the output frequency from the device. This allows the XR81112 to support a variety of applications. If the FSEL pins are left floating, the XR81112 will default (with internal pull-down resistors on the FSEL inputs) to the Frequency #1 output.

**Table 1: Output Frequency Selection**

| FSEL[1:0] | Output Frequency (MHz) |

|-----------|------------------------|

| 00        | Frequency #1           |

| 01        | Frequency #2           |

| 10        | Frequency #3           |

| 11        | Frequency #4           |

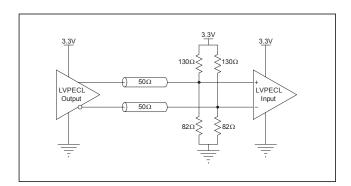

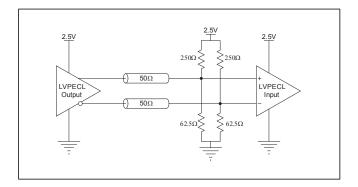

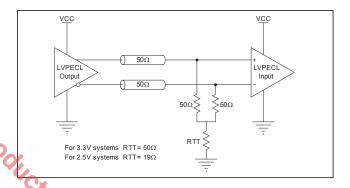

Termination for LVPECL Outputs

The termination schemes shown in Figure 5 and Figure 6 are typical for LVPECL outputs. Matched impedance layout techniques should be used for the LVPECL output pairs to minimize any distortion that could impact your maximum operating frequency. Figure 7 is an alternate termination scheme that uses a Y-termination approach.

Figure 5: XR81112 3.3V LVPECL Output Termination

Figure 6: XR81112 2.5V LVPECL Output Termination

Figure 7: XR81112 Alternate LVPECL Output Termination **Using Y-termination**

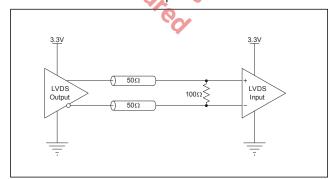

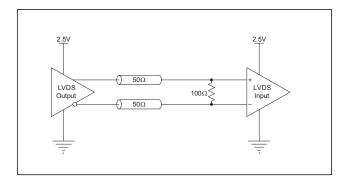

#### Termination for LVDS Outputs

The termination schemes shown in Figure 8 and Figure 9 are typical for LVDS outputs. LVDS swing is a small, typically 350mV, on 1.2V of common mode. The LVDS output pair needs a  $100\Omega$  resistor across the differential pair as close to the destination as possible.

Figure 8: XR81112 3.3V LVDS Output Termination

Figure 9: XR81112 2.5V LVDS Output Termination

#### **Output Signal Timing Definitions**

The following diagrams clarify the common definitions of the AC timing measurements.

Figure 10: Output Rise/Fall Time and Swing

Figure 11: Output Period and Duty Cycle

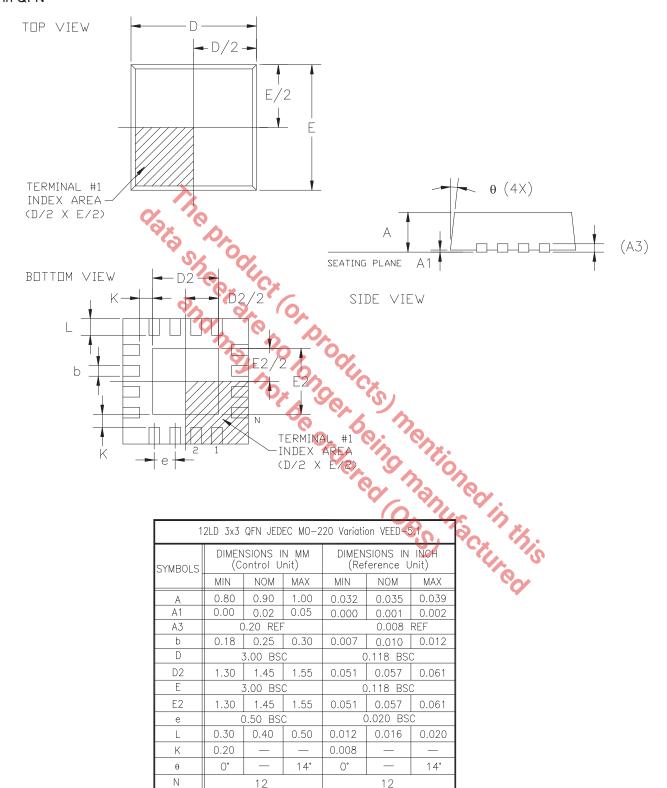

#### **Mechanical Dimensions**

#### 12-Pin QFN

3

3

ND

ΝE

3

3

#### **Ordering Information**

| Part Number | Package    | Green | Operating Temperature<br>Range | Shipping Packaging | Marking |

|-------------|------------|-------|--------------------------------|--------------------|---------|

| XR81112-F   | 12-pin QFN | Yes   | -40°C to +85°C                 | Tube/Tray          | T112    |

| XR81112EVB  | Eval Board | N/A   | N/A                            | N/A                | N/A     |

#### **Revision History**

| Revision                                                   | Date                                      | <b>À</b>            | Description                              |

|------------------------------------------------------------|-------------------------------------------|---------------------|------------------------------------------|

| 1A                                                         | June 2014                                 | Initial release.    | - 1                                      |

|                                                            |                                           | 0,00                |                                          |

|                                                            |                                           | 700                 | 40.                                      |

|                                                            |                                           | dy cox              |                                          |

|                                                            |                                           | 10/                 | P                                        |

|                                                            |                                           | 179                 | The no longer being manufactin this exar |

|                                                            |                                           |                     | no on der                                |

|                                                            |                                           |                     | b Ser is                                 |

|                                                            |                                           |                     | o beine                                  |

|                                                            |                                           |                     | de la lin                                |

|                                                            |                                           |                     | led he her                               |

|                                                            |                                           |                     | Canus in                                 |

|                                                            |                                           |                     | Son Roy The                              |

| For Further Assist                                         | tance:                                    |                     | July 15                                  |

| Email: commtechsu                                          | pport@exar.com                            |                     | FXAR                                     |

| Exar Technical Doo                                         | cumentation: http://www.e                 | exar.com/techdoc/   |                                          |

| Exar Corporation F<br>48720 Kato Road<br>Fremont, CA 95438 | leadquarters and Sales (<br>Tel: +1 (510) | Offices<br>668-7000 | A New Direction in Mixed-Signal          |

## **EXAR** A New Direction in Mixed-Signal

#### **NOTICE**

EXAR Corporation reserves the right to make changes to the products contained in this publication in order to improve design, performance or reliability. EXAR Corporation assumes no responsibility for the use of any circuits described herein, conveys no license under any patent or other right, and makes no representation that the circuits are free of patent infringement. Charts and schedules contained herein are only for illustration purposes and may vary depending upon a user's specific application. While the information in this publication has been carefully checked; no responsibility, however, is assumed for inaccuracies.

EXAR Corporation does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless EXAR Corporation receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of EXAR Corporation is adequately protected under the circumstances.

Reproduction, in part or whole, without the prior written consent of EXAR Corporation is prohibited.