### A Comparision between Exar's XR-88C681 and Motorola's MC2681 DUART Devices.

#### Introduction

This Applications Note briefly summarizes the differences between the XR-88C681 and the Motorola MC2681 DUART devices.

In general, these two device appear to be very compatible with each other. Their pin outs for both the 44 pin PLCC and 40 pin DIP packages are exactly the same. There are, however, some firmware (programming) differences between the two devices, that must be addressed by the user, if alternate sourcing between these two devices is to be achieved. Some of these differences between the XR-88C681 and the MC2681 are presented below.

#### 1. XR-88C681's Z-Mode

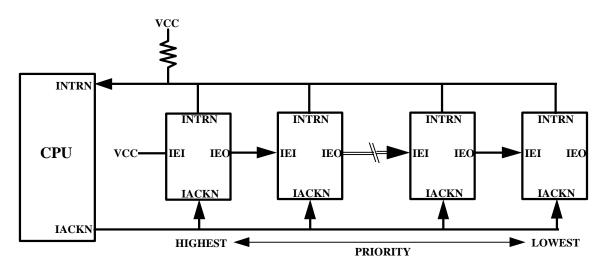

The XR-88C681 allows the user to Command the DUART into the Z-Mode (sometimes referred to as the "Zilog" Mode). This mode can be useful if the user wishes to daisy chain a series of DUART's together, as shown in Figure 1.

### Figure 1, An Illustration of XR-88C681 devices operating in a Daisy Chain, when commanded into the Z-Mode.

A more detailed discussion of the XR-88C681's Z Mode operation can be found in the Data Sheet. However, for the sake of this report, let's just say that the Z-Mode is a manner which allows several DUARTs to be configured in a Daisy Chain, as presented in

Figure 1, and allows the CPU to perform Vectored Interrupt Processing and Interrupt Prioritization for all of the DUART devices.

The MC2681 does not offer the Z-Mode of operation.

#### 2. Register Addressing

Both of these DUARTs contain registers that can be read from or written to. Each of these registers can be accessed by specifying its address via the 4 Address Bit Inputs. This access of the DUART Registers via the Address Inputs is referred to as "Register Addressing".

The Register Addressing between these two devices are slightly difference. Please note that some of these DUART registers are "Read Only" registers, and some are "Write Only" registers. Therefore, the Register Addressing comparison is based on "Read Mode" Register Access and "Write Mode" Register Access. Table 1 presents the DUART Address and the corresponding "Read" mode registers that the will be accessed for each of these two devices.

| Table 1, Register Addressing of | "Read Mode" | " Registers for the XR-88C681 and the |

|---------------------------------|-------------|---------------------------------------|

|                                 | MC2681 dev  | vices                                 |

| DU | DUART Address Bits |    |    | DUART Device/Read Mode Registers |                             |  |

|----|--------------------|----|----|----------------------------------|-----------------------------|--|

| A3 | A2                 | A1 | AO | XR-88C681                        | MC2681                      |  |

| 0  | 0                  | 0  | 0  | Mode Registers, Channel A        | Mode Registers, Channel A   |  |

|    |                    |    |    | (MR1A, MR2A)                     | (MR1A, MR2A)                |  |

| 0  | 0                  | 0  | 1  | Status Register, Channel A,      | Status Register, Channel A, |  |

|    |                    |    |    | (SRA)                            | (SRA)                       |  |

| 0  | 0                  | 1  | 0  | Masked Interrupt Status          | Do not access               |  |

|    |                    |    |    | Register (MISR)                  |                             |  |

| 0  | 0                  | 1  | 1  | Receiver Holding Register,       | Receiver Holding Register,  |  |

|    |                    |    |    | Channel A (RHRA)                 | Channel A (RHRA)            |  |

| 0  | 1                  | 0  | 0  | Input Port Change Register       | Input Port Change Register  |  |

|    |                    |    |    | (IPCR)                           | (IPCR)                      |  |

| 0  | 1                  | 0  | 1  | Interrupt Status Register        | Interrupt Status Register   |  |

|    |                    |    |    | (ISR)                            | (ISR)                       |  |

| 0  | 1                  | 1  | 0  | Counter/Timer Upper Byte         | Counter/Timer Upper Byte    |  |

|    |                    |    |    | Register (CTUR)                  | Register (CTUR)             |  |

| 0  | 1                  | 1  | 1  | Counter/Timer Lower Byte         | Counter/Timer Lower Byte    |  |

|    |                    |    |    | Register (CTLR)                  | Register (CTLR)             |  |

| 1  | 0                  | 0  | 0  | Mode Registers, Channel B        | Mode Registers, Channel B   |  |

|    |                    |    |    | (MR1B, MR2B)                     | (MR1B, MR2B)                |  |

| 1  | 0                  | 0  | 1  | Status Register, Channel B       | Status Register, Channel B  |  |

|    |                    |    |    | (SRB)                            | (SRB)                       |  |

| 1  | 0                  | 1  | 0  | RESERVED                         | Do Not Access               |  |

| 1  | 0                  | 1  | 1  | Receiver Holding Register,       | Receiver Holding Register,  |  |

|    |                    |    |    | Channel B (RHRB)                 | Channel B (RHRB)            |  |

| 1  | 1                  | 0  | 0  | Interrupt Vector Register        | Do Not Access               |  |

| 1  | 1                  | 0  | 1  | Input Port                       | Input Port                  |  |

| 1  | 1                  | 1  | 0  | Start Counter Command            | Start Counter Command       |  |

| 1  | 1                  | 1  | 1  | Stop Counter Command             | Stop Counter Command        |  |

Note: Differences between these two devices are in Bold-Italics Shaded boxes denote "Address Triggered" Commands

Table 2 presents the DUART Address and the corresponding "Write" mode Register that will be accessed for each of these two devices.

# Table 2, Register Addressing of "Write Mode" Registers for both the XR-88C681 and the MC2681 devices

| DUA | ART A | ddress | s Bits | DUART Devices/W                                   | rite Mode Registers                               |

|-----|-------|--------|--------|---------------------------------------------------|---------------------------------------------------|

| A3  | A2    | A1     | A0     | XR-88C681                                         | MC2681                                            |

| 0   | 0     | 0      | 0      | Mode Registers, Channel A<br>(MR1A, MR2A)         | Mode Registers, Channel A<br>(MR1A, MR2A)         |

| 0   | 0     | 0      | 1      | Clock Select Register, Channel<br>A (CSRA)        | Clock Select Register, Channel<br>A (CSRA)        |

| 0   | 0     | 1      | 0      | Command Register, Channel A (CRA)                 | Command Register, Channel A (CRA)                 |

| 0   | 0     | 1      | 1      | Transmitter Holding Register,<br>Channel A (THRA) | Transmitter Holding Register,<br>Channel A (THRA) |

| 0   | 1     | 0      | 0      | Auxiliary Control Register,<br>(ACR)              | Auxiliary Control Register,<br>(ACR)              |

| 0   | 1     | 0      | 1      | Interrupt Mask Register,<br>(IMR)                 | Interrupt Mask Register,<br>(IMR)                 |

| 0   | 1     | 1      | 0      | Counter/Timer Upper Byte<br>Register (CTUR)       | Counter/Timer Upper Byte<br>Register (CTUR)       |

| 0   | 1     | 1      | 1      | Counter/Timer Lower Byte<br>Register (CTLR)       | Counter/Timer Lower Byte<br>Register (CTLR)       |

| 1   | 0     | 0      | 0      | Mode Registers, Channel B<br>(MR1B, MR2B)         | Mode Registers, Channel B<br>(MR1B, MR2B)         |

| 1   | 0     | 0      | 1      | Clock Select Register, Channel<br>B, (CSRB)       | Clock Select Register, Channel<br>B, (CSRB)       |

| 1   | 0     | 1      | 0      | Command Register, Channel B<br>(CRB)              | Command Register, Channel B<br>(CRB)              |

| 1   | 0     | 1      | 1      | Transmitter Holding Register,<br>Channel B (THRB) | Transmitter Holding Register,<br>Channel B (THRB) |

| 1   | 1     | 0      | 0      | Interrupt Vector Register<br>(IVR)                | Do Not Access                                     |

| 1   | 1     | 0      | 1      | Output Port Configuration<br>Register (OPCR)      | Output Port Configuration<br>Register (OPCR)      |

| 1   | 1     | 1      | 0      | Set Output Port Bits<br>Command                   | Set Output Port Bits<br>Command                   |

| 1   | 1     | 1      | 1      | Clear Output Port Bits<br>Command                 | Clear Output Port Bits<br>Command                 |

Note: Differences between these two devices are in Bold-Italics Shaded boxes denote "Address Triggered" Commands.

#### 3. Command Register Bit Formats

For both of these DUART devices, each Channel contains an associated Command Register. In general, the Channel Command Register can be written to in order "Enable or Disable the Transmitter and/or Receiver". However, there are numerous "Miscellaneous" Commands which can be invoked by writing to the Channel Command Register.

The Command Register Bit Formats are slightly different between the XR-88C681 and the MC2681 devices. Tables 3 and 4 present a summary of the Bit Formats for the Command Registers, for each of these devices, respectively. Please note that this information applies to both Channels A and B.

#### Table 3, Bit Format of Command Register (Channels A and B) for the XR-88C681 Device

| Bit 7 | Bit 6                  | Bit 5           | Bit 4           | Bit 3                           | Bit 2           | Bit 1 | Bit 0                    |  |

|-------|------------------------|-----------------|-----------------|---------------------------------|-----------------|-------|--------------------------|--|

| N     | Miscellaneous Commands |                 |                 |                                 | Transmitter     |       | <b>Receiver Commands</b> |  |

|       |                        | Commands        |                 |                                 |                 |       |                          |  |

|       | See Table 5            |                 |                 |                                 | 00 = No Change  |       | 00 = No Change           |  |

|       |                        |                 | 01 = Enable Tx  |                                 | 01 = Enab       | le Rx |                          |  |

|       |                        | 10 = Disable Tx |                 | 10 = Disable Rx                 |                 |       |                          |  |

|       |                        |                 | 11 = Do Not Use |                                 | 11 = Do Not Use |       |                          |  |

|       |                        |                 |                 | (Indeterminate) (Indeterminate) |                 | nate) |                          |  |

#### Table 4, Bit Format of Command Register (Channels A and B) for the MC2681 Device

| Bit 7* | Bit 6                  | Bit 5       | Bit 4       | Bit 3                           | Bit 2                    | Bit 1          | Bit 0   |

|--------|------------------------|-------------|-------------|---------------------------------|--------------------------|----------------|---------|

|        | Miscellaneous Commands |             | Transmitter |                                 | <b>Receiver Commands</b> |                |         |

|        |                        |             |             | Commands                        |                          |                |         |

| Not    |                        | See Table 5 | í           | 00 = No Change                  |                          | 00 = No Change |         |

| Used   |                        |             |             | 01 = Enable Tx                  |                          | 01 = Enab      | le Rx   |

|        |                        |             |             | 10 = Disable Tx                 |                          | 10 = Disat     | ole Rx  |

|        |                        |             |             | 11 = Do Not Use                 |                          | 11 = Do N      | lot Use |

|        |                        |             |             | (Indeterminate) (Indeterminate) |                          | nate)          |         |

\* Bit 7 is not used and may be set to either zero or one.

Both Tables 3 and 4 call for Table 5 where the Bit Formats for the Miscellaneous Commands are defined for both the XR-88C681 and the MC2681 devices. Please note that the XR-88C681 uses four bits out of the Command Registers for the Miscellaneous Commands; whereas, the MC2681 only uses three bits out of the Command Register. When writing to one of the Command Registers of the MC2681 device, the Most Significant Bit (MSB) is interpreted as a "Don't Care". Consequently only 8 different Miscellaneous Commands are available from the MC2681. In contrast, 14 different Miscellaneous Commands are available with the XR-88C681 device. The commands listed in Table 5 applies to both Channels A and B, unless otherwise specified.

# Table 5, Bit Formats for the Miscellaneous Commands (CRn[7:4]) in the CommandRegisters for both the XR-88C681 and the MC2681 Devices

| Bit 7 | Bit 6 | Bit 5 | Bit 4 | XR-88C681                  | MC2681                |

|-------|-------|-------|-------|----------------------------|-----------------------|

| 0     | 0     | 0     | 0     | Null Command               | Null Command          |

| 0     | 0     | 0     | 1     | Reset MR Pointer           | Reset MR Pointer      |

| 0     | 0     | 1     | 0     | Reset Receiver             | Reset Receiver        |

| 0     | 0     | 1     | 1     | Reset Transmitter          | Reset Transmitter     |

| 0     | 1     | 0     | 0     | Reset Error Status         | Reset Error Status    |

| 0     | 1     | 0     | 1     | Reset Channel's Break      | Reset Channel's Break |

|       |       |       |       | Change Interrupt           | Change Interrupt      |

| 0     | 1     | 1     | 0     | Start Break                | Start Break           |

| 0     | 1     | 1     | 1     | Stop Break                 | Stop Break            |

| 1     | 0     | 0     | 0     | Set Receiver BRG Select    | Null Command          |

|       |       |       |       | Extend Bit                 |                       |

| 1     | 0     | 0     | 1     | Clear Receiver BRG Select  | Reset MR Pointer      |

|       |       |       |       | Extend Bit                 |                       |

| 1     | 0     | 1     | 0     | Set Transmitter BRG Select | Reset Receiver        |

|       |       |       |       | Extend Bit                 |                       |

| 1     | 0     | 1     | 1     | Clear Transmitter BRG      | Reset Transmitter     |

|       |       |       |       | Select Extend Bit          |                       |

| 1     | 1     | 0     | 0     | Channel A: Set Standby     | Reset Error Status    |

|       |       |       |       | Mode*                      |                       |

|       |       |       |       | Channel B: Reset IUS       |                       |

|       | _     |       |       | Latch*                     |                       |

| 1     | 1     | 0     | 1     | Channel A: Set Active      | Reset Channel's Break |

|       |       |       |       | Mode*                      | Change Interrupt      |

|       |       |       | -     | Channel B: Set Z-Mode*     |                       |

| 1     | 1     | 1     | 0     | Reserved - do not invoke   | Start Break           |

| -     | -     | -     | -     | during operation           |                       |

| 1     | 1     | 1     | 1     | Reserved - do not invoke   | Stop Break            |

|       |       |       |       | during operation           |                       |

\* This is a chip level command (e.g., effects the operation of both channels). Hence this command is invoked only if written to the specified Channel Command Register.

#### 4. Bit Rate Selection

Table 5 presented several Miscellaneous Commands that are available in the XR-88C681 device. However, these commands are not available in the MC2681 device. Some of these commands which effect Bit Rate Selection are presented below:

- Set Receiver BRG Select Extend Bit

- Clear Receiver BRG Select Extend Bit

- Set Transmitter BRG Select Extend Bit

- Clear Transmitter BRG Select Extend Bit

These BRG Select Extend Bits provide additional de-multiplexing of the range of bit rates that are available to the user. Consequently, the XR-88C681 is able to provide the user with 23 different standard bit rates from the Bit Rate Generator portion of the Timing Control Block. In contrast, the MC2681 is able to provide the user with 18 different standard bit rates from the Bit Rate Generator. For more details into the role of the BRG Select Extend Bits, please see the XR-68C681/88C681 Data Sheet.