# 22V, 15A Synchronous Step Down COT Power Module

### **General Description**

The XR79115 is a 15A synchronous step-down Power Module for point-of load supplies. A wide 5V to 22V input voltage range allows for single supply operation from industry standard 5V, 12V, and 19.6V rails.

With a proprietary emulated current mode Constant On-Time (COT) control scheme, the XR79115 provides extremely fast line and load transient response using ceramic output capacitors. It requires no loop compensation, hence simplifying circuit implementation and reducing overall component count. The control loop also provides 0.35% load and 0.1% line regulation and maintains constant operating frequency. A selectable power saving mode allows the user to operate in discontinuous mode (DCM) at light current loads, thereby significantly increasing the converter efficiency. With a 96% peak efficiency and 90% for loads as low as 100mA, the XR79115 is suitable for applications where low power losses are important.

A host of protection features, including over-current, over-temperature, short-circuit and UVLO, help achieve safe operation under abnormal operating conditions.

The XR79115 is available in a RoHS compliant, green / halogen free space-saving 68-pin 12 x 12 x 4mm QFN package. With integrated controller, drivers, bootstrap diode and capacitor, MOSFETs, inductor, CIN and COUT, this solution allows the smallest possible 15A POL design.

#### FEATURES

- Controller, drivers, bootstrap diode and capacitor, MOSFETs, inductor, CIN and COUT integrated in one package

- 15A step down module

□ Wide 5V to 22V input voltage range

□ ≥0.6V adjustable output voltage

- Proprietary Constant On-Time control

No loss componential required

- No loop compensation required

Stable ceramic output capacitor operation

- Dragrammable 200ns to 200 on time

- □ Programmable 200ns to 2µs on-time

- □ Constant 400kHz to 600kHz frequency

- Selectable CCM or CCM / DCM

- CCM / DCM for high efficiency at light-load

CCM for constant frequency at light-load

- Programmable hiccup current limit with thermal compensation

- Precision enable and Power Good flag

- Programmable soft-start

- 68-pin 12 x 12 x 4mm QFN package

#### APPLICATIONS

- Networking and communications

- Fast transient Point-of-Loads

- Industrial and medical equipment

- Embedded high power FPGA

Ordering Information - back page

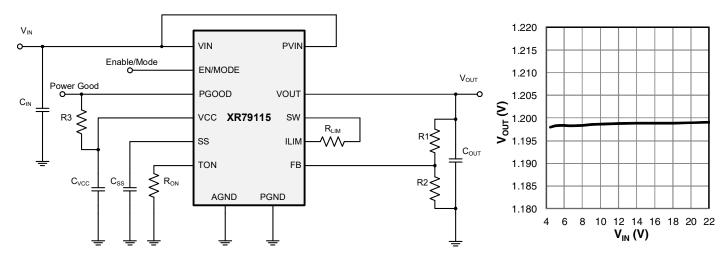

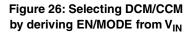

# Typical Application

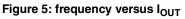

Line Regulation

# **Absolute Maximum Ratings**

Stresses beyond the limits listed below may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

| PV <sub>IN</sub> , V <sub>IN</sub>   | 0.3V to 25V               |

|--------------------------------------|---------------------------|

| V <sub>CC</sub>                      | 0.3V to 6.0V              |

| BST                                  | 0.3V to 31V <sup>1</sup>  |

| BST-SW                               | 0.3V to 6V                |

| SW, ILIM                             | 1V to 25V <sup>1, 2</sup> |

| ALL other pins                       | -0.3V to VCC+0.3V         |

| Storage temperature                  | 65°C to +150°C            |

| Junction temperature                 | 150°C                     |

| Power dissipation                    | Internally Limited        |

| Lead temperature (Soldering, 10 sec) | 260°C MSL3                |

| ESD Rating (HBM - Human Body Model)  | 2kV                       |

# **Operating Conditions**

| $PV_{IN}$ 3V to 22V                                                   |

|-----------------------------------------------------------------------|

| V <sub>IN</sub>                                                       |

| V <sub>CC</sub> 4.5V to 5.5V                                          |

| SW, ILIM1V to 22V <sup>1</sup>                                        |

| PGOOD, $V_{CC}$ , $T_{ON}$ , SS, EN, FB0.3V to 5.5V                   |

| Switching frequency400kHz to 600kHz <sup>3</sup>                      |

| Junction temperature range40°C to +125°C                              |

| JEDEC51 Package thermal resistance, $\theta_{JA}15.4^\circ\text{C/W}$ |

| Package power dissipation at 25°C6.5W                                 |

Note 1: No external voltage applied.

Note 2: The SW pin's minimum DC range is -1V, transient is -5V for less than 50ns.

Note 3: Recommended frequency for optimum performance.

# **Electrical Characteristics**

Unless otherwise noted:  $T_J = 25^{\circ}C$ ,  $V_{IN} = 12V$ , BST =  $V_{CC}$ , SW = AGND = PGND = 0V,  $C_{VCC} = 4.7\mu$ F. Limits applying over the full operating temperature range are denoted by a " $_{\bullet}$ "

| Symbol              | Parameter                                          | Conditions                                              |   | Min | Тур | Max | Units |  |

|---------------------|----------------------------------------------------|---------------------------------------------------------|---|-----|-----|-----|-------|--|

| Power Sup           | Power Supply Characteristics                       |                                                         |   |     |     |     |       |  |

| N/                  | Input voltage range                                | VCC regulating                                          | • | 5   |     | 22  | v     |  |

| V <sub>IN</sub>     |                                                    | VCC tied to VIN                                         | • | 4.5 |     | 5.5 |       |  |

| I <sub>VIN</sub>    | VIN input supply current                           | Not switching, $V_{IN} = 12V$ , $V_{FB} = 0.7V$         | • |     | 0.7 | 2   | mA    |  |

| Ivcc                | VCC quiescent current                              | Not switching, $V_{CC} = V_{IN} = 5V$ , $V_{FB} = 0.7V$ | • |     | 0.7 | 2   | mA    |  |

| I <sub>VIN</sub>    | VIN input supply current                           | f=500kHz, R <sub>ON</sub> = 61.9kΩ, VFB = 0.58V         |   |     | 17  |     | mA    |  |

| I <sub>OFF</sub>    | Shutdown current                                   | Enable = 0V, V <sub>IN</sub> = 12V                      |   |     | 1   |     | μA    |  |

| Enable and          | Enable and Under-Voltage Lock-Out UVLO             |                                                         |   |     |     |     |       |  |

| V <sub>IH_EN</sub>  | EN pin rising threshold                            |                                                         | • | 1.8 | 1.9 | 2.0 | V     |  |

| V <sub>EN_HYS</sub> | EN pin hysteresis                                  |                                                         |   |     | 50  |     | mV    |  |

| V <sub>IH_EN</sub>  | EN pin rising threshold for<br>DCM / CCM operation |                                                         | • | 2.8 | 3.0 | 3.1 | V     |  |

| V <sub>EN_HYS</sub> | EN pin hysteresis                                  |                                                         |   |     | 100 |     | mV    |  |

| Symbol               | Parameter                             | Conditions                                                        |   | Min      | Тур   | Max   | Units |

|----------------------|---------------------------------------|-------------------------------------------------------------------|---|----------|-------|-------|-------|

|                      | VCC UVLO start threshold, rising edge |                                                                   | • | 4.00     | 4.25  | 4.40  | V     |

|                      | VCC UVLO hysteresis                   |                                                                   |   |          | 200   |       | mV    |

| Reference            | e Voltage                             |                                                                   | • | •        |       |       |       |

|                      |                                       | V <sub>IN</sub> = 5V to 22V, VCC regulating                       |   | 0.597    | 0.600 | 0.603 | V     |

|                      |                                       | $V_{IN} = 4.5V$ to 5.5V, VCC tied to VIN                          |   | 0.596    | 0.600 | 0.604 | V     |

| V <sub>REF</sub>     | Reference voltage                     | V <sub>IN</sub> = 5V to 22V, VCC regulating                       |   |          |       | 1     | v     |

|                      |                                       | $V_{IN} = 4.5V$ to 5.5V, VCC tied to VIN                          | • | 0.594    | 0.600 | 0.606 |       |

|                      | DC line regulation                    | CCM, closed loop, $V_{IN}$ = 4.5V - 22V, applies to any $C_{OUT}$ |   |          | ±0.10 |       | %     |

|                      | DC load regulation                    | CCM, closed loop, $I_{OUT} = 0A - 15A$ , applies to any $C_{OUT}$ |   |          | ±0.35 |       | %     |

| Programm             | nable Constant On-Time                | 1                                                                 |   | <b>I</b> |       |       |       |

| T <sub>ON(MIN)</sub> | Minimum programmable on-time          | $R_{ON} = 6.98 k\Omega, V_{IN} = 22 V$                            |   |          | 120   |       | ns    |

| T <sub>ON2</sub>     | On-time 2                             | $R_{ON} = 6.98 k\Omega, V_{IN} = 12 V$                            | • | 156      | 192   | 228   | ns    |

|                      | f corresponding to on-time 2          | V <sub>OUT</sub> = 1.0V                                           |   | 450      | 535   | 660   | kHz   |

| T <sub>ON3</sub>     | On-time 3                             | R <sub>ON</sub> = 16.2kΩ, V <sub>IN</sub> = 12V                   | • | 341      | 412   | 483   | ns    |

|                      | Minimum off-time                      |                                                                   | • |          | 250   | 350   | ns    |

| Diode En             | nulation Mode                         |                                                                   |   |          |       |       |       |

|                      | Zero crossing threshold               | DC value measured during test                                     |   |          | -2    |       | mV    |

| Soft-start           |                                       |                                                                   |   |          |       |       |       |

|                      | SS charge current                     |                                                                   | • | -14      | -10   | -6    | μA    |

|                      | SS discharge current                  | Fault present                                                     | • | 1        |       |       | mA    |

| VCC Line             | ear Regulator                         |                                                                   |   |          |       |       |       |

|                      | VCC output voltage                    | $V_{IN} = 6V$ to 22V, $I_{LOAD} = 0$ to 30mA                      | • | 4.8      | 5.0   | 5.2   | V     |

|                      | voo ouput vonage                      | $V_{IN} = 5V$ , $I_{LOAD} = 0$ to 20mA                            | • | 4.6      | 4.8   |       | V     |

| Power Go             | ood Output                            |                                                                   |   |          |       |       |       |

|                      | Power Good threshold                  |                                                                   |   | -10      | -7.5  | -5    | %     |

|                      | Power Good hysteresis                 |                                                                   |   |          | 2     | 4     | %     |

|                      | Power Good sink current               |                                                                   |   | 1        |       |       | mA    |

| Protection           | n: OCP, OTP, Short-Circuit            | 1                                                                 |   | 1        | 1     |       |       |

|                      | Hiccup timeout                        |                                                                   |   |          | 110   |       | ms    |

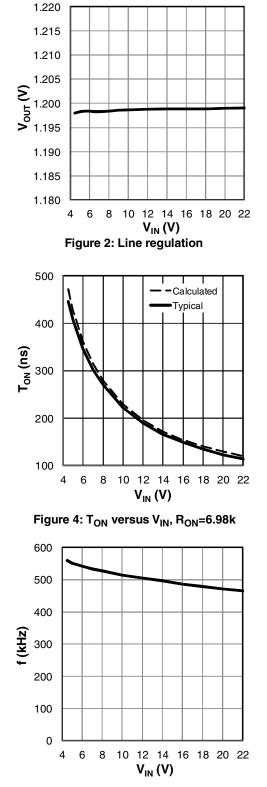

|                      | ILIM pin source current               |                                                                   |   | 45       | 50    | 55    | μA    |

|                      | ILIM current temperature coefficient  |                                                                   |   |          | 0.4   |       | %/°C  |

|                      | OCP comparator offset                 |                                                                   | • | -8       | 0     | +8    | mV    |

| Symbol            | Parameter                                  | Conditions                                                                    |          | Min  | Тур  | Max  | Units |

|-------------------|--------------------------------------------|-------------------------------------------------------------------------------|----------|------|------|------|-------|

|                   | Current limit blanking                     | GL rising > 1V                                                                |          |      | 100  |      | ns    |

|                   | Thermal shutdown threshold <sup>1</sup>    | Rising temperature                                                            |          |      | 150  |      | °C    |

|                   | Thermal hysteresis <sup>1</sup>            |                                                                               |          |      | 15   |      | °C    |

|                   | VSCTH feedback pin short-circuit threshold | Percent of V <sub>REF</sub> , short circuit is active after PGOOD is asserted | •        | 50   | 60   | 70   | %     |

| Output Po         | wer Stage                                  |                                                                               | <u> </u> |      | 1    | 1    |       |

| D                 | High-side MOSFET R <sub>DSON</sub>         |                                                                               |          |      | 8.3  | 10   | mΩ    |

| R <sub>DSON</sub> | Low-side MOSFET R <sub>DSON</sub>          | $I_{DS} = 2A, V_{GS} = 4.5V$                                                  |          |      | 4.2  | 5    | mΩ    |

| I <sub>OUT</sub>  | Maximum output current                     |                                                                               | •        | 15   |      |      | А     |

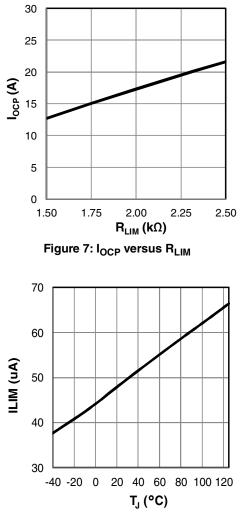

| L                 | Output inductance                          |                                                                               |          | 0.45 | 0.56 | 0.67 | uH    |

| C <sub>IN</sub>   | Input capacitance                          |                                                                               |          |      | 1    |      | uF    |

| C <sub>OUT</sub>  | Output capacitance                         |                                                                               |          |      | 2.2  |      | uF    |

| C <sub>BST</sub>  | Bootstrap capacitance                      |                                                                               |          |      | 0.1  |      | uF    |

Note 1: Guaranteed by design

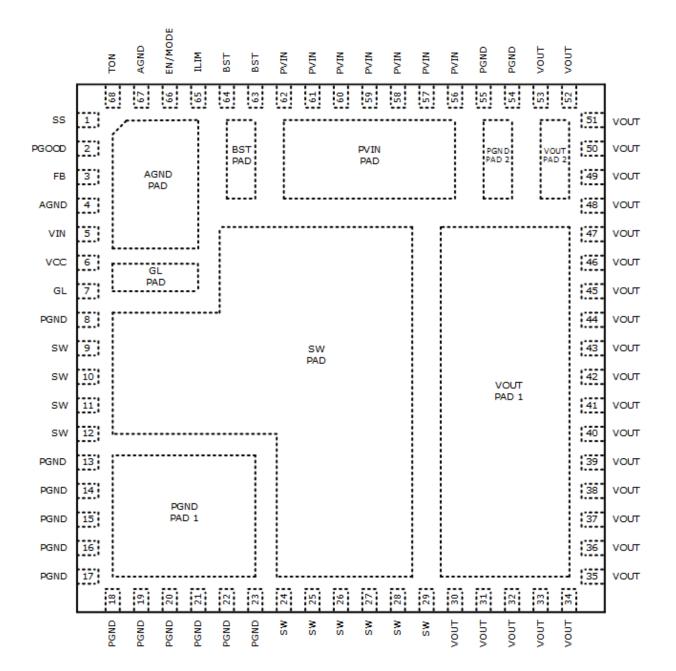

Pin Configuration, Top View

# **Pin Assignments**

| Pin No.                        | Pin Name | Туре  | Description                                                                                                                                                                                             |  |  |  |

|--------------------------------|----------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 1                              | SS       | A     | Soft-start pin. Connect an external capacitor between SS and AGND to program the soft-start rate based on the $10\mu$ A internal source current.                                                        |  |  |  |

| 2                              | PGOOD    | OD, O | Power-Good output. This open-drain output is pulled low when $V_{OUT}$ is outside the regulation                                                                                                        |  |  |  |

| 3                              | FB       | A     | Feedback input to feedback comparator. Connect with a set of resistors to VOUT and AGN order to program VOUT.                                                                                           |  |  |  |

| 4, 67,<br>AGND Pad             | AGND     | A     | Analog ground. Control circuitry of the IC is referenced to this pin.                                                                                                                                   |  |  |  |

| 5                              | VIN      | PWR   | IC supply input. Provides power to the internal LDO.                                                                                                                                                    |  |  |  |

| 6                              | VCC      | PWR   | The output of LDO. Bypass with a $4.7\mu F$ capacitor to AGND. For operation from a $5V_{IN}$ rail, VCC should be tied to VIN.                                                                          |  |  |  |

| 7, GL pad                      | GL       | 0     | Driver output for low-side N-channel synchronous MOSFET. It is internally connected to the gate of the FET. Leave this pin floating.                                                                    |  |  |  |

| 8                              | PGND     | PWR   | Controller low-side driver ground. Connect with a short trace to the closest PGND pins or PGND pad.                                                                                                     |  |  |  |

| 13-23,<br>54, 55,<br>PGND pads | PGND     | PWR   | Ground of the power stage. Should be connected to the system's power ground plane.                                                                                                                      |  |  |  |

| 9-12, 24-29,<br>SW Pad         | SW       | PWR   | Switching node. It is internally connected. Use thermal vias and / or sufficient PCB land area in order to heatsink the low-side FET and the inductor.                                                  |  |  |  |

| 30-53,<br>VOUT pads            | VOUT     | PWR   | Output of the power stage. Place the output filter capacitors as close as possible to these pins.                                                                                                       |  |  |  |

| 56-62,<br>PVIN Pad             | PVIN     | PWR   | Power stage input voltage. Place the input filter capacitors as close as possible to these pins.                                                                                                        |  |  |  |

| 63, 64,<br>BST Pad             | BST      | A     | Controller high-side driver supply pin. It is internally connected to SW via a 0.1µF bootstrap capacitor. Leave these pins floating.                                                                    |  |  |  |

| 65                             | ILIM     | А     | Over-current protection programming. Connect with a short trace to the SW pins.                                                                                                                         |  |  |  |

| 66                             | EN/MODE  | I     | Precision enable pin. Pulling this pin above 1.9V will turn the IC on and it will operate in Forced CCM. If the voltage is raised above 3.0V, then the IC will operate in DCM or CCM depending on load. |  |  |  |

| 68                             | TON      | А     | Constant on-time programming pin. Connect with a resistor to AGND.                                                                                                                                      |  |  |  |

Type: A = Analog, I = Input, O = Output, I/O = Input/Output, PWR = Power, OD = Open-Drain

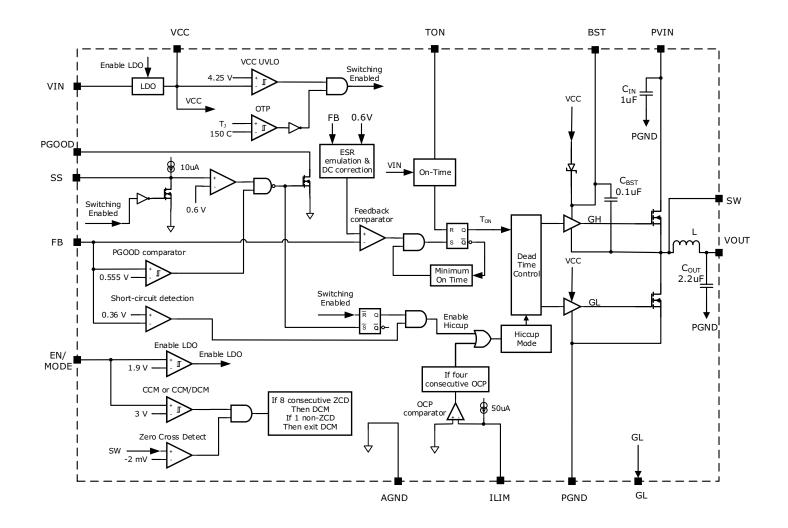

# **Functional Block Diagram**

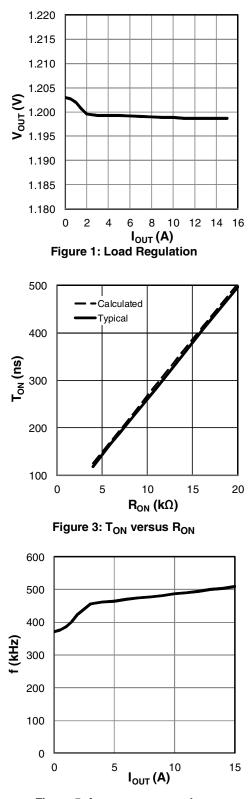

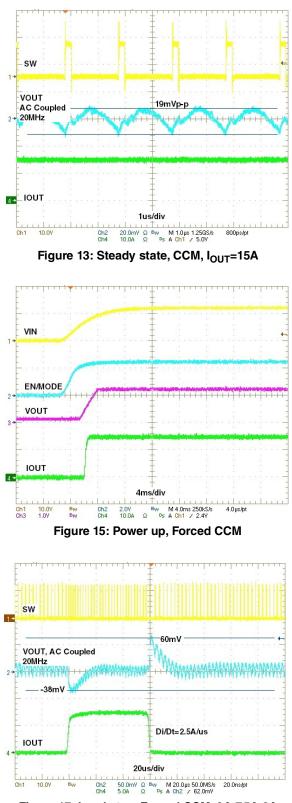

# **Typical Performance Characteristics**

Unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 15A$ , f = 500kHz,  $T_A = 25^{\circ}$ C. The schematic is from the application information section.

Figure 6: frequency versus V<sub>IN</sub>

# **Typical Performance Characteristics**

Unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 15A$ , f = 500kHz,  $T_A = 25^{\circ}$ C. The schematic is from the application information section.

Figure 9: I<sub>LIM</sub> versus temperature

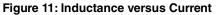

Figure 8: V<sub>REF</sub> versus temperature

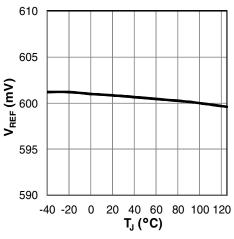

Figure 10: T<sub>ON</sub> versus temperature, R<sub>ON</sub>=16.2k $\Omega$

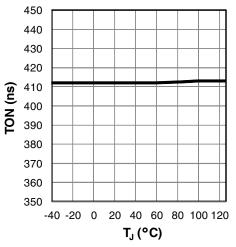

Figure 12: Maximum recommended  $V_{OUT}$  versus f,  $V_{IN}$ =12V

# **Typical Performance Characteristics**

Unless otherwise noted:  $V_{IN} = 12V$ ,  $V_{OUT} = 1.2V$ ,  $I_{OUT} = 15A$ , f = 500kHz,  $T_A = 25^{\circ}C$ . The schematic is from the application information section.

Figure 17: Load step, Forced CCM, 0A-7.5A-0A

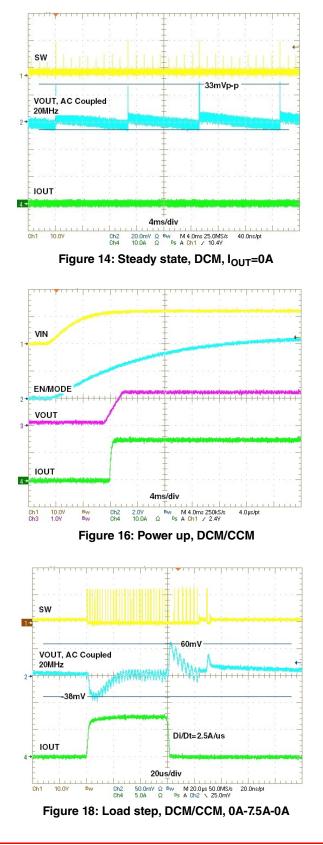

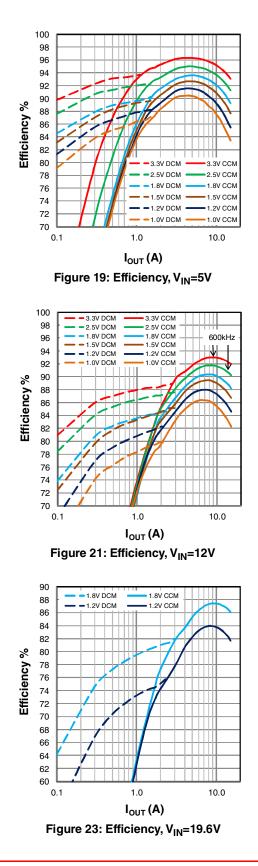

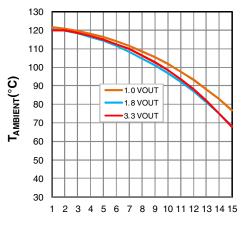

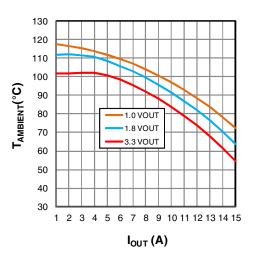

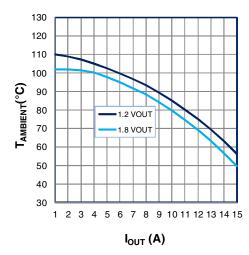

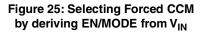

# **Efficiency and Package Thermal Derating**

Unless otherwise noted:  $T_{AMBIENT} = 25^{\circ}C$ , no air flow, f = 500kHz, the schematic is from the application information section.

I<sub>OUT</sub> (Α) Figure 20: Maximum T<sub>AMBIENT</sub> vs I<sub>OUT</sub>, V<sub>IN</sub>=5V

Figure 22: Maximum  $T_{AMBIENT}$  vs  $I_{OUT}, V_{IN}{=}12V$

Figure 24: Maximum T<sub>AMBIENT</sub> vs I<sub>OUT</sub>, V<sub>IN</sub>=19.6V

## **Functional Description**

The XR79115 is a synchronous step-down, proprietary emulated current-mode Constant On-Time (COT) module. The on-time, which is programmed via  $R_{ON}$ , is inversely proportional to  $V_{IN}$  and maintains a nearly constant frequency. The emulated current-mode control is stable with ceramic output capacitors.

Each switching cycle begins with the GH signal turning on the high-side (switching) FET for a preprogrammed time. At the end of the on-time, the high-side FET is turned off and the low-side (synchronous) FET is turned on for a preset minimum time (250ns nominal). This parameter is termed Minimum Off-Time. After the Minimum Off-Time, the voltage at the feedback pin FB is compared to an internal voltage ramp at the feedback comparator. When V<sub>FB</sub> drops below the ramp voltage, the high-side FET is turned on and the cycle repeats. This voltage ramp constitutes an emulated current ramp and makes possible the use of ceramic capacitors, in addition to other capacitor types, for output filtering.

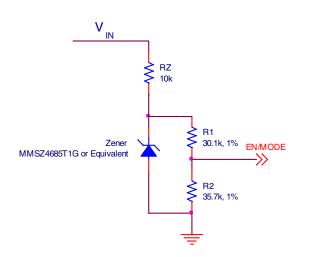

#### Enable / Mode Input (EN/MODE)

The EN/MODE pin accepts a tri-level signal that is used to control turn on and turn off. It also selects between two modes of operation: 'Forced CCM' and 'DCM / CCM'. If EN/MODE is pulled below 1.8V, the module shuts down. A voltage between 2.0V and 2.8V selects the Forced CCM mode, which will run the module in continuous conduction at all times. A voltage higher than 3.1V selects the DCM / CCM mode, which will run the module in discontinuous conduction at light loads.

#### Selecting the Forced CCM Mode

In order to set the module to operate in Forced CCM, a voltage between 2.0V and 2.8V must be applied to EN/MODE. This can be achieved with an external control signal that meets the above voltage requirement. Where an external control is not available, the EN/MODE can be derived from  $V_{IN}$ . If  $V_{IN}$  is well regulated, use a resistor divider and set the voltage to 2.5V. If  $V_{IN}$  varies over a wide range, the circuit shown in Figure 25 can be used to generate the required voltage. Note that at  $V_{IN}$  of 5V and 22V, the nominal Zener voltage is 3.8V and 4.7V, respectively. Therefore for  $V_{IN}$  in the range of 5V to 22V, the circuit shown in Figure 25 will generate the  $V_{EN}$  required for Forced CCM.

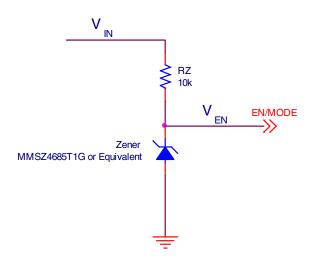

#### Selecting the DCM / CCM Mode

In order to set the module operation to DCM / CCM, a voltage between 3.1V and 5.5V must be applied to the EN/MODE pin. If an external control signal is available, it can be directly connected to EN/MODE. In applications

where an external control is not available, the EN/MODE input can be derived from  $V_{IN}$ . If  $V_{IN}$  is well regulated, use a resistor divider and set the voltage to 4V. If  $V_{IN}$  varies over a wide range, the circuit shown in Figure 26 can be used to generate the required voltage.

## Programming the On-Time

The on-time  $T_{ON}$  is programmed via resistor  $R_{ON}$  according to following equation:

$$\mathsf{R}_{\mathsf{ON}} = \frac{\mathsf{V}_{\mathsf{IN}} \times [\mathsf{T}_{\mathsf{ON}} - (25 \times 10^{-9})]}{2.85 \times 10^{-10}}$$

where  $\mathsf{T}_{\mathsf{ON}}$  is calculated from:

$$\mathsf{T}_{\mathsf{ON}} = \frac{\mathsf{V}_{\mathsf{OUT}}}{\mathsf{V}_{\mathsf{IN}} \times f \times \mathit{Eff}}$$

Where:

f is the desired switching frequency at nominal  $\mathsf{I}_{\mathsf{OUT}}$

Eff is the Module efficiency corresponding to nominal  ${\rm I}_{\rm OUT}$  shown in Figures 19, 21, 23

Substituting for  $T_{ON}$  in the first equation we get:

$$\mathsf{R}_{\mathsf{ON}} = \frac{\left(\frac{\mathsf{V}_{\mathsf{OUT}}}{f \times \textit{Eff}}\right) - \left[(25 \times 10^{-9}) \times \mathsf{V}_{\mathsf{IN}}\right]}{2.85 \times 10^{-10}}$$

## **Over-Current Protection (OCP)**

If load current exceeds the programmed over-current  $I_{OCP}$  for four consecutive switching cycles, then the module enters the hiccup mode of operation. In hiccup mode, the MOSFET gates are turned off for 110ms (hiccup timeout). Following the hiccup timeout, a soft-start is attempted. If OCP persists, the hiccup timeout will repeat. The module will remain in hiccup mode until the load current is reduced below the programmed  $I_{OCP}$ . In order to program the overcurrent protection, use the following equation:

$$\mathsf{RLIM} = \frac{(\mathsf{I}_{\mathsf{OCP}} \times \mathsf{RDS}) + \mathsf{8mV}}{\mathsf{ILIM}}$$

Where:

RLIM is resistor value for programming  $\mathsf{I}_{\mathsf{OCP}}$

I<sub>OCP</sub> is the over-current threshold to be programmed

RDS is the MOSFET rated on-resistance  $(5m\Omega)$

8mV is the OCP comparator maximum offset

ILIM is the internal current that generates the necessary OCP comparator threshold (use  $45\mu$ A).

Note that ILIM has a positive temperature coefficient of 0.4%/°C (Figure 9). This is meant to roughly match and compensate for the positive temperature coefficient of the synchronous FET. A graph of typical I<sub>OCP</sub> versus RLIM is shown in Figure 7.

## Short-Circuit Protection (SCP)

If the output voltage drops below 60% of its programmed value, the module will enter hiccup mode. Hiccup will persist until the short-circuit is removed. The SCP circuit becomes active after PGOOD asserts high.

## Over-Temperature (OTP)

OTP triggers at a nominal die temperature of 150°C. The gates of the switching FET and synchronous FET are turned off. When die temperature cools down to 135°C, soft-start is initiated and operation resumes.

## Programming the Output Voltage

Use an external voltage divider as shown in the Application Circuit to program the output voltage  $V_{\mbox{OUT}}.$

$$R1 = R2 \times \left(\frac{V_{OUT}}{0.6} - 1\right)$$

where R2 has a nominal value of  $2k\Omega$ .

## Programming the Soft-start

Place a capacitor CSS between the SS and AGND pins to program the soft-start. In order to program a soft-start time of TSS, calculate the required capacitance CSS from the following equation:

$$CSS = TSS \times \left(\frac{10 \mu A}{0.6 V}\right)$$

## Feed-Forward Capacitor (C<sub>FF</sub>)

A feed-forward capacitor (C<sub>FF</sub>) may be necessary, depending on the Equivalent Series Resistance (ESR) of C<sub>OUT</sub>. If only ceramic output capacitors are used for C<sub>OUT</sub>, then a C<sub>FF</sub> is necessary. Calculate C<sub>FF</sub> from:

$$C_{FF} = \frac{1}{2 \times \pi \times 80 \, kHz \times R1}$$

where:

R1 is the resistor that  $C_{FF}$  is placed in parallel with

80kHz is the location of the Zero formed by R1 and  $C_{\text{FF}}$

Note that minimum required  $C_{OUT}$  is 140 $\mu$ F when using ceramic capacitors.

When using capacitors with higher ESR, such as the PANASONIC TPE series, a  $C_{FF}$  is not required provided following conditions are met:

1. The frequency of output filter LC double-pole  $\rm f_{\rm LC}$  should be less than 15kHz.

2. The frequency of ESR Zero  $f_{\text{Zero},\text{ESR}}$  should be at least three times larger than  $f_{\text{LC}}.$

As an example the application circuit has  $f_{LC} = 8.3$ kHz and  $f_{Zero,ESR} = 23.4$ kHz.

Note that the steady-state voltage ripple at feedback pin FB ( $V_{FB,RIPPLE}$ ) must not exceed 50mV in order for the module to function correctly. If  $V_{FB,RIPPLE}$  is larger than 50mV, then  $C_{OUT}$  should be increased as necessary in order to keep the  $V_{FB,RIPPLE}$  below 50mV.

## Feed-Forward Resistor (R<sub>FF</sub>)

Poor PCB layout can cause FET switching noise at the output and may couple to the FB pin via  $C_{FF}$ . Excessive noise at FB will cause poor load regulation. To solve this problem, place a resistor  $R_{FF}$  in series with  $C_{FF}$ . An  $R_{FF}$  value up to 2% of R1 is acceptable.

# **Application Circuit**

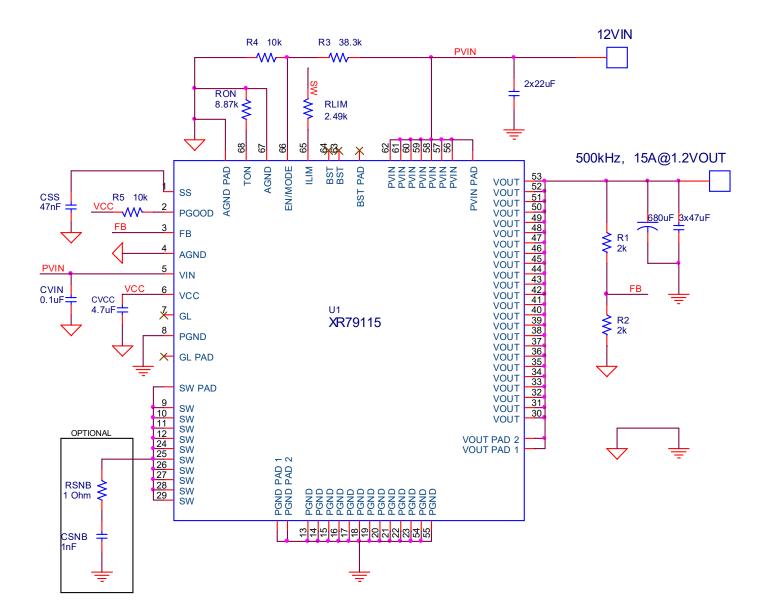

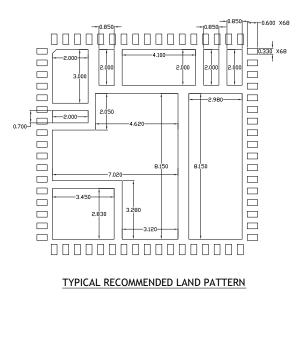

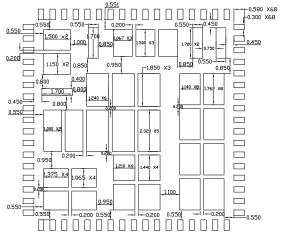

## **Mechanical Dimensions**

Revision: B

#### TYPICAL RECOMMENDED STENCIL

NDTE : ALL DIMENSIONS ARE IN MILLIMETERS, ANGLES ARE IN DEGREES.

Drawing No.: POD-00000075 Revision: B

# Ordering Information<sup>(1)</sup>

| Part Number | Operating Temperature Range | Lead-Free          | Package     | Packaging Method |  |  |  |

|-------------|-----------------------------|--------------------|-------------|------------------|--|--|--|

| XR79115EL-F | -40°C to +125°C             | Yes <sup>(2)</sup> | 12x12mm QFN | Tray             |  |  |  |

| XR79115EVB  | XR79115 Evaluation Board    |                    |             |                  |  |  |  |

NOTE:

1. Refer to www.maxlinear.com/XR79115 for most up-to-date Ordering Information.

2. Visit www.maxlinear.com for additional information on Environmental Rating.

## **Revision History**

| Revision | Date          | Description                                                                                                             |

|----------|---------------|-------------------------------------------------------------------------------------------------------------------------|

| 1A       | December 2014 | ECN 1451-09                                                                                                             |

| 1B       | January 2015  | Corrected schematic on page 1, ECN 1504-06                                                                              |

| 1C       | June 2018     | Update to MaxLinear logo. Update format and Ordering Information format.                                                |

| 1D       | November 2019 | Correct block diagram by changing the input gate that connects to the Hiccup Mode block from an AND gate to an OR gate. |

#### **Corporate Headquarters:** 5966 La Place Court Suite 100 Carlsbad, CA 92008 Tel.:+1 (760) 692-0711 Fax: +1 (760) 444-8598

www.maxlinear.com

The content of this document is furnished for informational use only, is subject to change without notice, and should not be construed as a commitment by MaxLinear, Inc. Max-Linear, Inc. assumes no responsibility or liability for any errors or inaccuracies that may appear in the informational content contained in this guide. Complying with all applicable copyright laws is the responsibility of the user. Without limiting the rights under copyright, no part of this document may be reproduced into, stored in, or introduced into a retrieval system, or transmitted in any form or by any means (electronic, mechanical, photocopying, recording, or otherwise), or for any purpose, without the express written permission of MaxLinear, Inc.

Maxlinear, Inc. does not recommend the use of any of its products in life support applications where the failure or malfunction of the product can reasonably be expected to cause failure of the life support system or to significantly affect its safety or effectiveness. Products are not authorized for use in such applications unless MaxLinear, Inc. receives, in writing, assurances to its satisfaction that: (a) the risk of injury or damage has been minimized; (b) the user assumes all such risks; (c) potential liability of MaxLinear, Inc. is adequately protected under the circumstances.

MaxLinear, Inc. may have patents, patent applications, trademarks, copyrights, or other intellectual property rights covering subject matter in this document. Except as expressly provided in any written license agreement from MaxLinear, Inc., the furnishing of this document does not give you any license to these patents, trademarks, copyrights, or other intellectual property.

MaxLinear, the MaxLinear logo, and any MaxLinear trademarks, MxL, Full-Spectrum Capture, FSC, G.now, AirPHY and the MaxLinear logo are all on the products sold, are all trademarks of MaxLinear, Inc. or one of MaxLinear's subsidiaries in the U.S.A. and other countries. All rights reserved. Other company trademarks and product names appearing herein are the property of their respective owners.

© 2014 - 2019 MaxLinear, Inc. All rights reserved